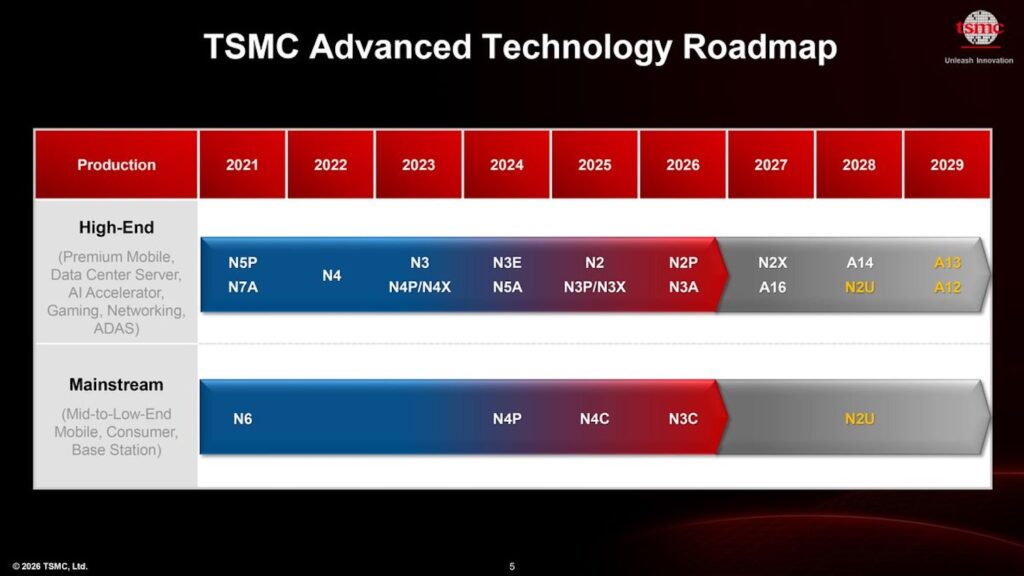

TSMC ha aprovechado su Technology Symposium 2026 para enseñar una hoja de ruta que va bastante más allá de una simple actualización incremental. La compañía taiwanesa ha puesto fecha y forma a la siguiente fase de su ofensiva en lógica avanzada, automoción y empaquetado para IA, con una secuencia que ya no se limita a los nombres conocidos de N2, A16 y A14, sino que añade nuevas piezas como N2U, A13, A12, N2A y una expansión muy agresiva de CoWoS, SoW-X y SoIC. El mensaje es claro: TSMC quiere seguir marcando el ritmo no solo en nodo, sino también en integración de memoria, apilado 3D y densidad de sistema.

La parte más relevante del anuncio no está solo en que TSMC siga avanzando, algo que ya se daba por hecho, sino en cómo ha ordenado su calendario hasta 2029. La compañía ha separado mejor su rama de evolución “estándar” y la orientada a backside power delivery, mientras acelera en packaging para responder a la presión real del mercado de IA. Visto en conjunto, el nuevo roadmap refuerza la sensación de que TSMC no quiere limitarse a ir por delante de Intel y Samsung, sino obligar a ambos a competir en varios frentes al mismo tiempo: proceso, potencia, memoria e integración.

N2U, A13 y A12: una hoja de ruta más diversificada

La primera novedad importante es N2U, una nueva extensión de la plataforma de 2 nm. Según TSMC, este nodo emplea optimización conjunta de diseño y tecnología para ofrecer entre un 3 % y un 4 % más de velocidad o entre un 8 % y un 10 % menos de consumo frente a N2P, además de una mejora de densidad lógica de 1,02x a 1,03x. La compañía lo sitúa como una opción equilibrada para IA, HPC y móvil, apoyada en la madurez y el rendimiento de fabricación de la plataforma de 2 nm, con producción prevista en 2028.

Junto a esa evolución, TSMC ha oficializado A13, que define como un shrink directo de A14. Sobre el papel, A13 ofrecerá un 6 % de ahorro de área respecto a A14, mantendrá compatibilidad total de reglas de diseño y sumará mejoras de eficiencia energética y rendimiento mediante optimización conjunta. La producción está prevista para 2029, un año después de A14. Esa compatibilidad de diseño no es un detalle menor: facilita la migración de clientes sin exigir una ruptura brusca con la generación anterior.

El tercer elemento de esta rama avanzada es A12, que TSMC presenta como una mejora de la plataforma A14 pensada para IA y HPC gracias a Super Power Rail, su tecnología de alimentación por la cara posterior del chip. La empresa la encuadra como una evolución orientada a resolver uno de los grandes cuellos de botella del silicio actual: la entrega de energía cuando la densidad y la demanda de corriente siguen subiendo. También en este caso, la producción está prevista para 2029.

Tabla: el nuevo mapa de TSMC hasta 2029

| Tecnología | Enfoque principal | Fecha prevista |

|---|---|---|

| N2U | Evolución de 2 nm con mejor equilibrio entre rendimiento, consumo y densidad | 2028 |

| A13 | Shrink de A14 con 6 % menos área y reglas compatibles | 2029 |

| A12 | Plataforma con Super Power Rail para IA y HPC | 2029 |

| N2A | Primer nodo automotive con nanosheets | 2028 (calificación AEC-Q100) |

| CoWoS 14 retículas | Hasta ~10 grandes dies de cómputo y 20 pilas HBM | 2028 |

| CoWoS >14 retículas | Expansión adicional del empaquetado | 2029 |

| SoW-X | Integración a escala wafer de más de 40 retículas | 2029 |

| A14-to-A14 SoIC | Apilado 3D con 1,8x más densidad de E/S die-to-die | 2029 |

Fuente: TSMC North America Technology Symposium 2026.

Automoción e IA física: TSMC también mueve ficha con N2A

TSMC no ha querido limitar la conversación a móvil o centros de datos. En el mismo evento anunció N2A, descrito como su primer proceso automotive con transistores nanosheet. La compañía afirma que ofrecerá entre un 15 % y un 20 % más de velocidad al mismo consumo frente a N3A y que completará la calificación AEC-Q100 en 2028. Además, TSMC integrará kits de diseño “Auto-Use” dentro del PDK de N2P para que los clientes puedan empezar antes sus desarrollos orientados a automoción.

Ese movimiento resulta especialmente relevante porque la automoción avanzada, los sistemas ADAS y la llamada IA física empiezan a necesitar nodos de primer nivel con garantías de fiabilidad más estrictas. Y ahí TSMC intenta adelantarse con una oferta específica, no solo con una adaptación tardía de sus nodos de consumo.

CoWoS, SoW-X y SoIC: donde se juega buena parte de la batalla de la IA

Si el roadmap lógico impresiona, el de empaquetado quizá dice aún más sobre el momento actual de la industria. TSMC confirmó que ya produce CoWoS de 5,5 retículas y que en 2028 llevará esa tecnología a 14 retículas, con capacidad para integrar aproximadamente 10 grandes dies de cómputo y 20 pilas HBM en un solo paquete. Después llegará una versión de más de 14 retículas en 2029. La compañía sitúa estos avances como respuesta directa a la necesidad de meter más cómputo y más memoria en un único encapsulado para cargas de IA.

A eso se suma SoW-X, la tecnología de sistema sobre oblea que TSMC prevé también para 2029 y que apunta a más de 40 retículas. Y, en el terreno del apilado 3D, TSMC anunció que A14-to-A14 SoIC estará listo para producción en 2029 con una densidad de E/S die-to-die 1,8 veces superior a la de N2-on-N2 SoIC. Ese dato no es cosmético: en IA, el ancho de banda interno y la proximidad física entre dies empiezan a ser tan importantes como el nodo litográfico.

Intel y Samsung siguen en la carrera, pero el listón sube

Sería exagerado decir que TSMC “ha borrado” toda esperanza de Intel y Samsung. Ambos siguen teniendo planes ambiciosos. Intel Foundry mantiene en su hoja de ruta Intel 18A, ya listo para proyectos de cliente, y Intel 14A, con PowerDirect como evolución de su backside power delivery, además de extensiones como 18A-P y 18A-PT. Samsung, por su parte, reafirmó en 2024 que sigue en pista para producción en 2 nm en 2025 y 1,4 nm en 2027.

Pero lo que sí hace TSMC con este roadmap es elevar la exigencia competitiva. Ya no basta con tener un nodo avanzado o con prometer backside power. El mercado quiere también empaquetado masivo para IA, hojas de ruta claras en automoción, integración con HBM y continuidad de diseño entre generaciones. En esa visión más amplia del negocio, TSMC sigue apareciendo como el actor que mejor coordina el conjunto del sistema.

Preguntas frecuentes

¿Qué ha anunciado exactamente TSMC en su roadmap hasta 2029?

TSMC ha presentado nuevas etapas de su hoja de ruta como N2U, A13, A12 y N2A, además de avances en empaquetado con CoWoS de 14 retículas, expansión a más de 14 retículas, SoW-X y A14-to-A14 SoIC para 2029.

¿Qué aporta A13 frente a A14?

Según TSMC, A13 es un shrink directo de A14 con un 6 % menos de área, compatibilidad total de reglas de diseño y mejoras adicionales de eficiencia y rendimiento. La producción está prevista para 2029.

¿Qué es N2U y por qué importa?

N2U es una nueva variante de la plataforma de 2 nm que promete entre 3-4 % más de velocidad o 8-10 % menos consumo frente a N2P, con una ligera mejora de densidad. Está prevista para 2028.

¿TSMC deja fuera a Intel y Samsung con esta hoja de ruta?

No de forma definitiva. Intel y Samsung mantienen sus propios planes avanzados, pero el roadmap de TSMC refuerza su liderazgo al combinar nodo, alimentación trasera, automoción y packaging avanzado dentro de una estrategia mucho más integrada.

vía: Toms Hardware y TSMC