Synopsys, Inc. (Nasdaq: SNPS) ha anunciado una colaboración ampliada con TSMC para el desarrollo de diseños en nodos avanzados, desplegados en una variedad de aplicaciones de inteligencia artificial, computación de alto rendimiento y móviles. La colaboración más reciente incluye un flujo co-optimizado de IC fotónicos, que aborda la aplicación de la tecnología de fotónica de silicio en la búsqueda de una mejor eficiencia energética, rendimiento y densidad de transistores.

Synopsys ha destacado la confianza de la industria en sus flujos de diseño digital y analógico, listos para producción en tecnologías de proceso TSMC N3/N3P y N2. Ambas compañías están colaborando en flujos de próxima generación impulsados por IA, incluyendo Synopsys DSO.ai™, para la productividad y optimización del diseño. Además, Synopsys está desarrollando una amplia cartera de IP de Fundación e Interfaz en TSMC N2/N2P. En un anuncio relacionado, Keysight, Synopsys y Ansys han presentado un nuevo flujo de migración de diseño de radiofrecuencia (RF) integrado desde el proceso N16 de TSMC a su tecnología N6RF+.

Acelerando la Innovación de Próxima Generación para Diseños en Nodos Avanzados de TSMC

«Los avances en los flujos EDA listos para producción de Synopsys y la integración de fotónica con nuestro 3DIC Compiler, que soporta el estándar 3Dblox, combinados con una amplia cartera de IP, permiten a Synopsys y TSMC ayudar a los diseñadores a alcanzar el siguiente nivel de innovación para sus diseños de chips en los procesos avanzados de TSMC,» dijo Sanjay Bali, vicepresidente de estrategia y gestión de productos para el Grupo EDA en Synopsys. «La profunda confianza que hemos construido a lo largo de décadas de colaboración con TSMC ha proporcionado a la industria soluciones EDA e IP críticas que ofrecen resultados de calidad y ganancias de productividad con una migración más rápida de nodo a nodo.»

«Nuestra estrecha colaboración con socios del ecosistema Open Innovation Platform (OIP)® como Synopsys ha permitido a los clientes abordar los requisitos de diseño más desafiantes, todo en la vanguardia de la innovación desde dispositivos a escala angstrom hasta sistemas multi-die complejos en una variedad de diseños de computación de alto rendimiento,» dijo Dan Kochpatcharin, jefe de la División de Gestión de Infraestructura de Diseño en TSMC. «Juntos, TSMC y Synopsys ayudarán a los equipos de ingeniería a crear la próxima generación de diseños diferenciados en los nodos de proceso más avanzados de TSMC con un tiempo de resultados más rápido.»

Flujos Digitales y Analógicos Certificados en Nodos Avanzados

Los flujos de diseño digital y analógico listos para producción de Synopsys para las tecnologías de proceso TSMC N3P y N2 se han desplegado en una variedad de diseños de IA, computación de alto rendimiento y móviles. El flujo de migración de diseño analógico impulsado por IA permite una rápida migración de un nodo de proceso a otro. Un nuevo flujo está disponible para la migración de TSMC N5 a N3E, sumándose a los flujos establecidos de Synopsys para los procesos TSMC N4P a N3E y N3E a N2.

Además, los kits de diseño de proceso interoperables (iPDKs) y los runsets de verificación física Synopsys IC Validator™ están disponibles para que los equipos de diseño transiten eficientemente a las tecnologías de proceso avanzadas de TSMC. Synopsys IC Validator permite la verificación física completa del chip para manejar la creciente complejidad de las reglas de verificación física. Synopsys IC Validator está ahora certificado en las tecnologías de proceso TSMC N2 y N3P.

Transmisión de Datos Más Rápida para Diseños Multi-Die con IC Fotónicos

El alto volumen de procesamiento de datos para el entrenamiento de IA requiere interconexiones de baja latencia, eficientes en energía y de alta banda ancha, impulsando la adopción de transceptores ópticos y ópticas empaquetadas cercanas/compuestas utilizando tecnología de fotónica de silicio. Synopsys y TSMC están desarrollando soluciones de flujo de extremo a extremo para diseños electrónicos y fotónicos multi-die utilizando la tecnología Compact Universal Photonic Engine (COUPE) de TSMC para mejorar el rendimiento y la función del sistema. Este flujo abarca el diseño de IC fotónicos con Synopsys OptoCompiler™ e integración con ICs eléctricos utilizando Synopsys 3DIC Compiler y tecnologías de análisis multifísico de Ansys.

Aceleración del Tiempo de Comercialización con una Amplia Cartera de IP N2 y N2P

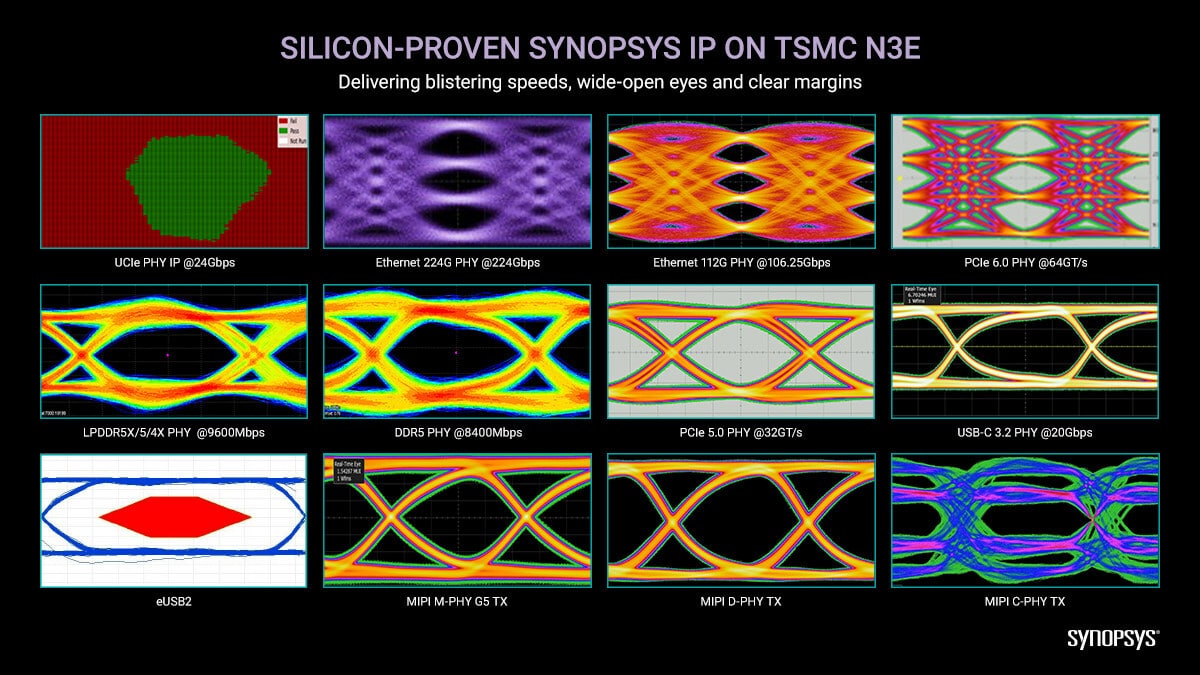

Synopsys está desarrollando una amplia cartera de IP de Fundación e Interfaz para las tecnologías de proceso TSMC N2 y N2P para permitir un éxito de silicio más rápido para complejos SoCs de IA, computación de alto rendimiento y móviles. La IP PHY de alta calidad en N2 y N2P, incluyendo UCIe, HBM4/3e, 3DIO, PCIe 7.x/6.x, MIPI C/D-PHY y M-PHY, USB, DDR5 MR-DIMM y LPDDR6/5x, permite a los diseñadores beneficiarse de las mejoras de PPA de los nodos de proceso más avanzados de TSMC. Además, Synopsys proporciona una cartera de IP de Fundación e Interfaz probada en silicio para TSMC N3P, incluyendo Ethernet 224G, UCIe, MIPI C/D-PHY y M-PHY, USB/DisplayPort y eUSB2, LPDDR5x, DDR5 y PCIe 6.x, con DDR5 MR-DIMM en desarrollo. La IP de Synopsys para procesos avanzados de TSMC ha sido adoptada por docenas de empresas líderes para acelerar su tiempo de desarrollo.