La industria de los semiconductores sigue avanzando, pero cada nuevo salto exige más tiempo, más dinero y más cambios de arquitectura. La vieja idea de que los transistores simplemente se hacían más pequeños generación tras generación ya no explica bien lo que está ocurriendo. En la era de los angstroms, la mejora vendrá de una mezcla mucho más compleja: nuevos transistores, apilado vertical, materiales alternativos, interconexiones más finas, alimentación por la parte trasera del wafer y empaquetado avanzado.

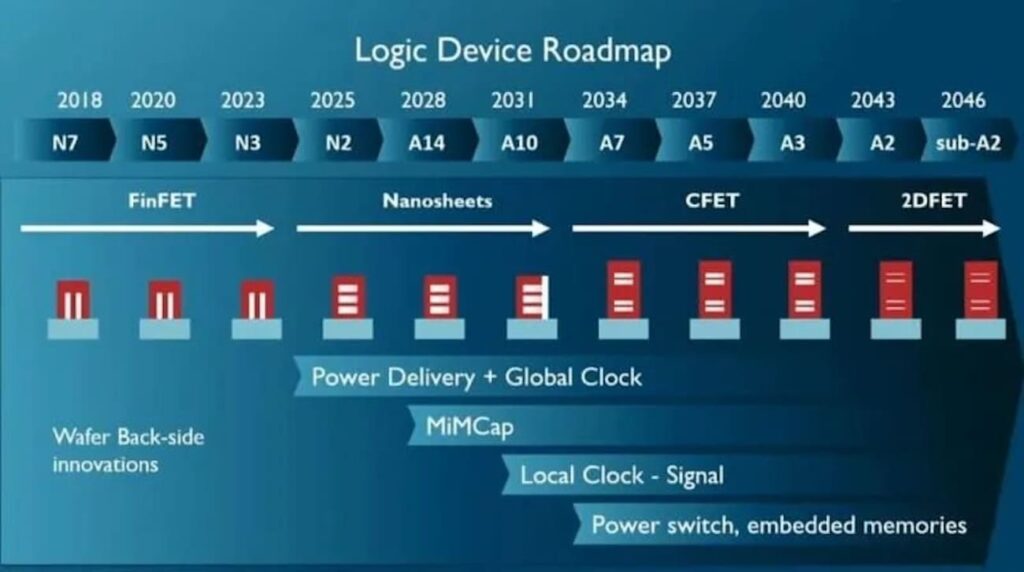

La hoja de ruta atribuida a imec, el centro belga de investigación en nanoelectrónica, sitúa el primer nodo por debajo de 1 nm alrededor de 2034. Ese punto estaría asociado al nodo A7, equivalente a 0,7 nm o 7 angstroms, y marcaría la entrada de los CFET, una arquitectura que apila verticalmente transistores de canal n y canal p para seguir aumentando la densidad lógica. Más adelante, hacia 2043, aparecerían los 2D FET en el nodo A2, con materiales bidimensionales como posible vía para continuar la miniaturización más allá de los límites actuales.

Conviene hacer una precisión importante: estas cifras no deben leerse como una promesa de producción comercial exacta. En semiconductores, los nombres de los nodos ya no describen una dimensión física literal del transistor, sino una etiqueta tecnológica y comercial. La hoja de ruta apunta a fases de investigación y desarrollo, no necesariamente a que un fabricante concreto vaya a vender chips de 0,7 nm en 2034 o de 0,2 nm en 2043. Aun así, el calendario ayuda a entender hacia dónde se mueve el sector.

Moore no ha muerto, pero ya no camina igual

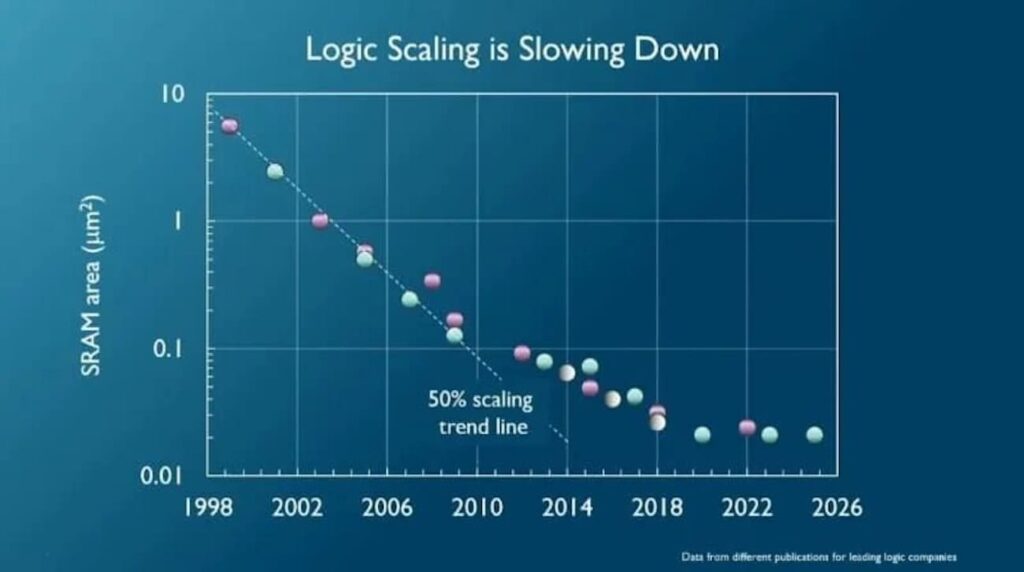

Durante décadas, la industria se apoyó en una reducción muy agresiva del tamaño de los transistores. Entre finales de los noventa y la primera década de los 2000, la densidad lógica mejoraba a un ritmo que hacía viable duplicar prestaciones o reducir costes con cada generación. Esa dinámica se ha frenado. La reducción del área de las celdas SRAM, uno de los indicadores más observados en la escalabilidad de los nodos, lleva años perdiendo velocidad y desde los nodos más recientes se mueve de forma mucho menos espectacular.

El problema no es solo físico. Fabricar en nodos punteros exige litografía EUV avanzada, procesos más complejos, más máscaras, más pasos de fabricación y una inversión enorme en fábricas. Por eso los grandes fabricantes y diseñadores de chips están recurriendo cada vez más a chiplets, 2,5D, 3D IC, interposers y empaquetado avanzado. En vez de meter todo en un único die gigantesco, se combinan bloques especializados fabricados en distintos nodos y conectados con técnicas cada vez más sofisticadas.

La inteligencia artificial y la computación de alto rendimiento han acelerado esa tendencia. Los aceleradores modernos no dependen únicamente de transistores más pequeños; también necesitan HBM cerca del procesador, interconexiones de muy alto ancho de banda, alimentación eficiente y disipación térmica bajo control. La carrera no está solo en el nodo, sino en todo el sistema.

Aun así, la lógica seguirá escalando. La hoja de ruta plantea una transición clara desde FinFET a nanosheet, después a CFET y, más adelante, a transistores basados en materiales 2D. Cada salto intenta resolver el mismo dilema: cómo aumentar densidad y rendimiento cuando la reducción horizontal tradicional ya no basta.

| Periodo aproximado | Nodo | Arquitectura prevista | Idea principal |

|---|---|---|---|

| 2018-2023 | N7, N5, N3 | FinFET | Última gran etapa de FinFET en nodos avanzados |

| 2025 | N2 | Nanosheet / GAA | Entrada de transistores gate-all-around |

| 2028 | A14 | Nanosheet mejorado | Más densidad y ajustes de arquitectura |

| 2031 | A10 | Nanosheet avanzado | Último tramo antes del sub-1 nm |

| 2034 | A7 | CFET | Primer nodo previsto por debajo de 1 nm |

| 2037 | A5 | CFET mejorado | Más escalado vertical y optimización |

| 2040 | A3 | CFET avanzado | Extensión de la arquitectura CFET |

| 2043 | A2 | 2D FET | Entrada de materiales bidimensionales |

| 2046 | Sub-A2 | 2D FET avanzado | Escenario de continuidad más allá de 0,2 nm |

CFET y 2D FET: la apuesta por apilar y cambiar materiales

El paso inmediato ya está en marcha con los nanosheet FET, también conocidos como GAA o gate-all-around. La idea es envolver el canal del transistor por todos los lados con la puerta, lo que mejora el control eléctrico frente a FinFET. TSMC, Samsung e Intel han ido preparando sus propias variantes de esta transición, cada uno con nombres comerciales y calendarios distintos.

La siguiente gran etapa sería CFET. En una arquitectura CFET, los transistores nMOS y pMOS se apilan uno encima del otro en lugar de colocarse en plano. Esto permite reducir el área de celda y aumentar la densidad sin depender únicamente de hacer todo más estrecho. imec ha señalado en publicaciones técnicas que CFET es una arquitectura atractiva para nodos más allá de 1 nm y ha trabajado en distintas vías de integración, incluidas opciones monolíticas y secuenciales.

El salto posterior llegaría con los 2D FET. Aquí ya no hablamos solo de reorganizar transistores de silicio, sino de introducir materiales bidimensionales en los canales de conducción. El atractivo está en que estos materiales pueden mantener propiedades eléctricas útiles a escalas extremadamente pequeñas. La dificultad es llevarlos a fabricación industrial con rendimiento, uniformidad, contacto eléctrico y fiabilidad suficientes. En investigación, el camino es prometedor; en producción masiva, todavía quedan muchos problemas por resolver.

Por eso el horizonte de 2043-2046 debe tratarse con prudencia. No es una fecha de lanzamiento de producto. Es una visión de investigación que marca los posibles escalones si la industria consigue resolver materiales, procesos, interconexión, alimentación y disipación.

El cuello de botella también está en las conexiones

Reducir el transistor no basta si las conexiones entre transistores se convierten en el límite. La parte BEOL, responsable de las capas metálicas que conectan los dispositivos, es una de las zonas más críticas. A medida que los pitches metálicos bajan, aumentan la resistencia, la congestión y los problemas térmicos. El cobre, que ha sido dominante durante años, empieza a tener dificultades a escalas muy pequeñas por la necesidad de barreras y por el volumen útil que se pierde.

La hoja de ruta apunta a un cambio progresivo hacia materiales como rutenio y técnicas como semi-damascene o metalización sustractiva, además de air gaps y vías autoalineadas. En los nodos cercanos a 2 nm se habla de pitches metálicos mínimos de 24 a 26 nm; en A14 bajarían a 20-22 nm; en A10 se moverían en torno a 18-20 nm, y en A7 podrían situarse en 16-18 nm. Para A5 y A3, el objetivo estaría en una horquilla de 12 a 16 nm, aunque todavía en fase de investigación.

| Año aproximado | Nodo | Pitch metálico mínimo | Tecnología BEOL destacada |

|---|---|---|---|

| 2025 | N2 | 24-26 nm | Cobre, dual/single damascene |

| 2028 | A14 | 20-22 nm | Mejora de procesos actuales |

| 2031 | A10 | 18-20 nm | Transición a rutenio, air gaps y vías autoalineadas |

| 2034 | A7 | 16-18 nm | Semi-damascene / metalización sustractiva |

| 2037 | A5/A3 | 12-16 nm | Materiales alternativos en investigación |

Este punto suele quedar fuera del debate público, más centrado en nombres como “2 nm” o “1,4 nm”, pero es decisivo. Un chip no mejora solo porque sus transistores sean más densos. Si la alimentación, las señales y la disipación no acompañan, el rendimiento real queda limitado o el consumo se dispara.

Alimentación por la parte trasera y el problema del calor

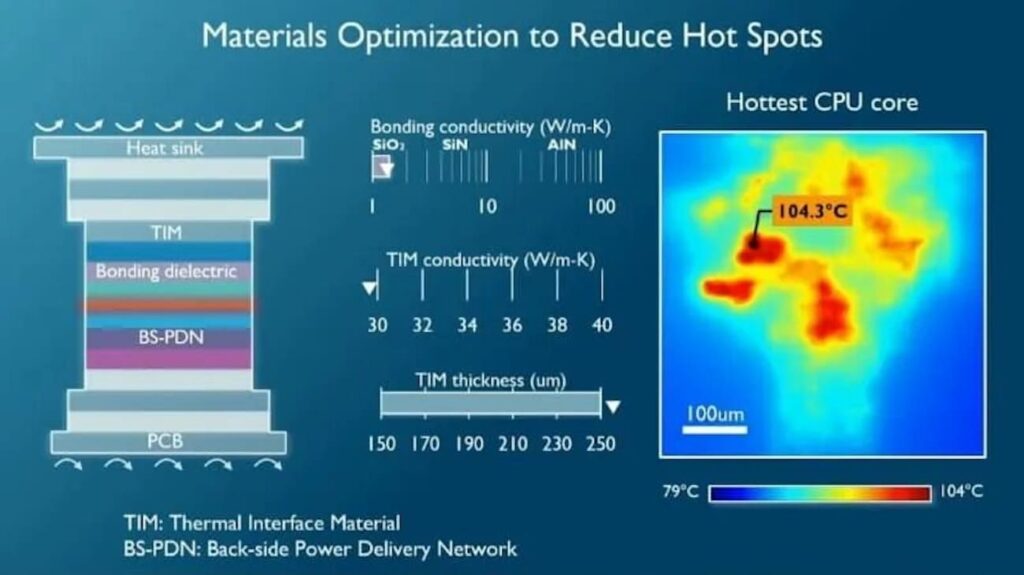

Otra pieza clave será la alimentación. Las redes tradicionales llevan señales y energía por la parte frontal del wafer, compartiendo espacio en muchas capas metálicas. La alimentación por la parte trasera, conocida como backside power delivery network o BSPDN, separa parte de esa red y libera espacio en el frontal para señales. La ventaja potencial es clara: menos congestión, mejor entrega de corriente y más margen para escalar.

Pero tampoco es gratis. Mover la red de alimentación modifica los caminos térmicos y puede complicar la disipación. El propio análisis técnico de imec sobre backside power delivery advierte de la necesidad de estudiar cuidadosamente las opciones de diseño y los compromisos térmicos. En chips de alto rendimiento, donde el calor ya es un límite serio, cada cambio en la estructura física tiene consecuencias.

La hoja de ruta también menciona la integración de reguladores de voltaje en la placa, el paquete, el interposer o incluso la parte trasera del wafer. En sistemas de IA y HPC, alimentar de forma estable paquetes con varios chiplets, HBM y aceleradores exige una arquitectura eléctrica mucho más precisa. La potencia ya no puede verse como un elemento externo al chip; empieza a formar parte del diseño avanzado del sistema.

Ese es el verdadero mensaje de la hoja de ruta. El futuro de los semiconductores no depende de una única tecnología milagrosa. Depende de coordinar transistores nuevos, cableado más eficiente, entrega de energía, materiales, empaquetado 3D, memoria cercana y disipación. La miniaturización continúa, pero ya no avanza sola.

La llegada de chips sub-1 nm, si se cumplen las previsiones, no será un simple cambio de nodo. Será el resultado de casi una década de preparación técnica desde los nanosheet actuales hasta CFET y, más adelante, materiales 2D. En paralelo, la industria tendrá que justificar económicamente cada salto. Con fábricas cada vez más caras y empaquetado avanzado ganando protagonismo, no todos los productos necesitarán el nodo más puntero.

Los grandes aceleradores de IA, CPUs de alto rendimiento y chips para centros de datos seguirán empujando la frontera. El resto del mercado probablemente combinará nodos maduros, chiplets y empaquetado para equilibrar coste y prestaciones. Moore sigue vivo, pero se ha vuelto más caro, más vertical y mucho más difícil de explicar en una sola cifra de nanómetros.

Preguntas frecuentes

¿Cuándo llegarán los chips por debajo de 1 nm?

La hoja de ruta atribuida a imec sitúa el primer nodo sub-1 nm alrededor de 2034, con A7 o 0,7 nm basado en CFET. No debe entenderse como una fecha garantizada de producción comercial.

¿Qué es un CFET?

Un CFET es un transistor complementario que apila verticalmente dispositivos nMOS y pMOS. Su objetivo es aumentar la densidad lógica más allá de lo que permiten los nanosheet convencionales.

¿Qué son los 2D FET?

Son transistores que usan materiales bidimensionales en el canal de conducción. Se estudian como una posible vía para extender la escalabilidad lógica hacia nodos de 0,2 nm y menores.

¿Por qué ya no basta con reducir el tamaño del transistor?

Porque los límites actuales también están en interconexiones, alimentación, calor, memoria y coste de fabricación. El rendimiento moderno depende cada vez más del diseño del sistema completo.

fuente: 36kr