TSMC ha aprovechado su Open Innovation Platform Ecosystem Forum para enviar un mensaje muy claro a toda la industria: en computación de alto rendimiento e inteligencia artificial, su apuesta se apoya en tres pilares que avanzan en paralelo —advanced silicon, advanced stacking y advanced packaging. No es solo marketing; detrás hay una hoja de ruta agresiva de nodos de 2 nm y más allá, nuevas celdas estándar NanoFlex y un ecosistema de empaquetado que ya está dando forma a la próxima generación de aceleradores de IA.

VSORA y su Jotunn 8: escaparate europeo del ecosistema TSMC

Uno de los ejemplos que TSMC ha puesto sobre la mesa es el de VSORA, una compañía francesa que se ha apoyado en el ecosistema de la foundry para desarrollar un acelerador de IA basado en RISC-V.

Su chip Jotunn 8 integra:

- 288 GB de memoria HBM3E

- Una ancho de banda de memoria de 8 TB/s

- Dos chiplets de computación con un total de 144.000 millones de transistores

- Una potencia de cálculo de 3,2 PFLOPS en FP8 denso

Los chiplets de cómputo se fabrican en nodo N5 de TSMC y el conjunto se integra mediante empaquetado CoWoS-S, en un package de aproximadamente 70 × 80 mm. Según la propia VSORA, el tiempo de desarrollo ha sido de unos 18 meses, un plazo muy ajustado para un diseño tan complejo, que ilustra hasta qué punto el ecosistema de diseño (EDA, IP, packaging) alrededor de TSMC está maduro para productos de IA de nueva generación.

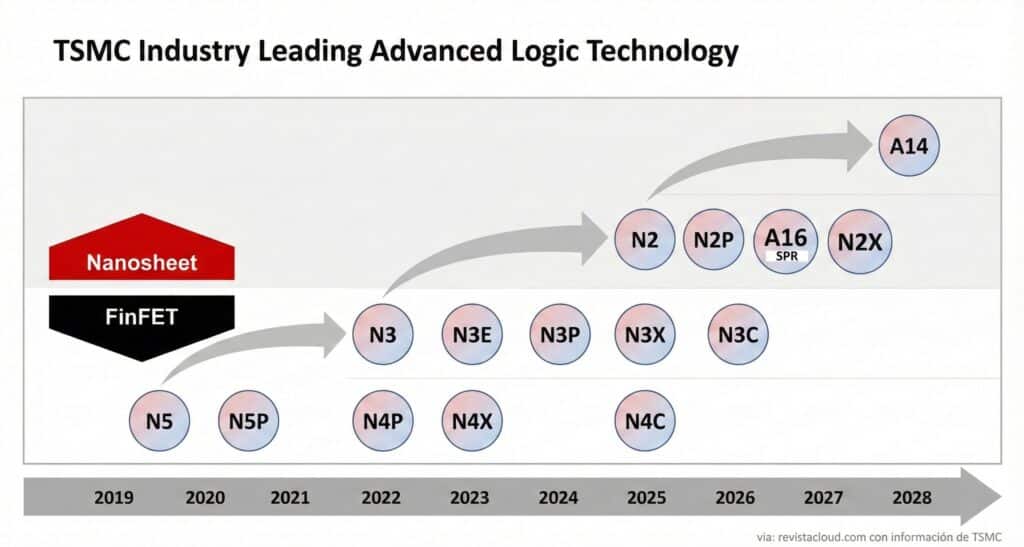

De N3 a N2, A16 y A14: la carrera más allá de los 2 nm

En el plano del silicio, TSMC está en plena transición desde la familia N3 (FinFET) hacia los nodos de 2 nm (N2), donde entra por fin en juego la arquitectura de transistores nanosheet (gate-all-around).

La compañía sitúa su hoja de ruta de la siguiente manera:

- N2: ya en rampa de producción en volumen para clientes punteros de HPC y móviles. Los primeros diseños han mostrado incrementos de rendimiento en torno al 16 % a la misma potencia y ahorros de energía superiores al 30 % frente a N3E, dependiendo del tipo de núcleo y biblioteca usada.

- N2P: evolución optimizada de N2 prevista para principios de 2026, con mejoras adicionales en rendimiento y eficiencia.

- A16: nuevo nodo que combina transistores nanosheet con alimentación trasera (backside power) bajo la denominación interna Super Power Rail (SPR), con los primeros chips previstos para finales de 2026.

- A14: siguiente paso sobre A16, con un diseño de nanosheet mejorado y una nueva vuelta de tuerca en rendimiento por vatio.

TSMC habla de una mejora de rendimiento a igual consumo de hasta 1,8× si se compara el salto completo desde N7 hasta A14, y de un aumento de eficiencia (más trabajo por vatio) de aproximadamente 4,2× en ese mismo recorrido. Entre N2 y A14, la foundry apunta a incrementos de frecuencia en torno al 16 % manteniendo la misma potencia, o bien reducciones de consumo con el mismo rendimiento.

Más cerca en el tiempo, el nodo A16 con SPR debería ofrecer un 8–10 % más de frecuencia a igual tensión frente a N2P, o bien una reducción de consumo del 15–20 % manteniendo el rendimiento, según las cifras internas que TSMC ha presentado a sus clientes.

NanoFlex: celdas estándar a medida del diseño

Una de las novedades más técnicas, pero clave para arquitectos de chips, es la introducción de la tecnología NanoFlex junto con la familia N2. NanoFlex permite mezclar y ajustar distintos tipos de celdas estándar dentro de un mismo diseño —más anchas y rápidas para rutas críticas, más compactas y eficientes para lógica menos exigente— sin penalizar el flujo de diseño.

Según ha explicado la compañía, este enfoque permite obtener chips hasta un 15 % más rápidos o un 30 % más eficientes simplemente eligiendo la combinación adecuada de bibliotecas dentro del mismo nodo.

En otras palabras, no se trata solo del nodo en sí, sino del “kit completo” de bibliotecas, reglas de diseño y herramientas habilitadas por TSMC para exprimir ese nodo en distintas direcciones: máximo rendimiento, máximo rendimiento por vatio o máximo rendimiento por milímetro cuadrado.

El papel de la alimentación trasera: de N2P a A16

Otro punto importante de la hoja de ruta es el movimiento estratégico de la alimentación trasera. Inicialmente, TSMC había vinculado el backside power delivery a N2P, pero las últimas actualizaciones desplazan esta innovación a A16, que se convierte de facto en el nodo donde confluyen nanosheets y alimentación trasera en la plataforma de 2 nm de la compañía.

La alimentación trasera libera área en la parte frontal del chip —donde se encuentran los transistores— al mover las líneas de potencia a la cara posterior de la oblea. Es una mejora que reduce resistencias e inductancias del suministro eléctrico, facilita alcanzar frecuencias más altas y abre la puerta a arquitecturas de chip más densas y modulares.

Empaquetado avanzado y apilado: CoWoS, HBM y 3D como norma

Más allá del silicio, TSMC deja claro que no basta con tener el “mejor nodo”: los grandes diseños de IA y HPC actuales dependen de un empaquetado avanzado que permita combinar múltiples chiplets de cómputo con varios stacks de memoria HBM en un único sistema.

En este terreno, la compañía domina con su familia de tecnologías 3DFabric, que agrupa:

- CoWoS (Chip-on-Wafer-on-Substrate), en variantes como CoWoS-S, utilizada en el Jotunn 8 de VSORA, o en muchas de las GPU de IA de última generación.

- SoIC y otras soluciones de apilado 3D para unir dies lógicos o de memoria con interconexiones de muy alta densidad.

- Empaquetados avanzados pensados específicamente para anchos de banda de memoria del orden de varios terabytes por segundo y consumos de cientos de vatios.

El resultado es que TSMC no solo fabrica el chip, sino que ofrece a los diseñadores una ruta integrada desde el tape-out hasta el módulo completo con HBM, interposer y sustrato listos para soldar en el servidor.

IA también dentro de la fábrica

La compañía también ha subrayado que la propia IA juega un papel interno en sus procesos: desde la fase de diseño lógico y verificación, pasando por la optimización de layout, hasta el control de fabricación en las fábricas y la fase de pruebas (testing).

Buena parte de estas técnicas se agrupaban hace años bajo el paraguas de machine learning, pero el aumento de la complejidad de los nodos de 3 nm y 2 nm ha convertido estos modelos en herramientas esenciales para mantener el rendimiento, el rendimiento por oblea y la calidad dentro de parámetros aceptables.

“No hay camino alrededor de TSMC” en HPC e IA

Visto en conjunto, el mensaje que deja el foro es contundente: en los próximos años, ningún diseñador fabless de chips de alto rendimiento e IA podrá ignorar a TSMC si quiere competir en la frontera tecnológica.

La foundry no solo ofrece los nodos más avanzados del mercado, sino que:

- Integra desde fases muy tempranas el trabajo con las principales herramientas EDA.

- Proporciona bibliotecas y tecnologías como NanoFlex para exprimir los nodos de 2 nm y posteriores.

- Domina el empaquetado avanzado necesario para combinar chiplets y HBM a gran escala.

- Ha alineado su hoja de ruta con las necesidades de entrenamiento e inferencia de modelos de IA cada vez más grandes.

Mientras Intel y Samsung Foundry tratan de recortar distancias en nodos y packaging, TSMC se ha colocado en una posición en la que controla a la vez el silicio, el apilado y el empaquetado de la próxima generación de hardware de IA. Y, a día de hoy, todo apunta a que esa combinación seguirá marcando el ritmo de la industria durante la próxima década.

vía: hardwareluxx