SK hynix ha enseñado su hoja de ruta más ambiciosa hasta la fecha durante el SK AI Summit 2025. No es un simple calendario de más capas y más MHz: es una visión centrada en la IA que abarca memoria de alto ancho de banda (HBM), DRAM convencional, NAND/SSD y nuevos bloques “inteligentes” que prometen llevar el cómputo más allá del muro de la memoria. La compañía separa dos etapas con objetivos muy claros:

- 2026–2028: despliegue agresivo de HBM4/HBM4E y la llegada de LPDDR6; optimizaciones de DRAM para reducir coste total en datacenter; salto a PCIe 6.0 en SSD.

- 2029–2031: consolidación y nueva ola con HBM5/HBM5E (estándar y a medida), DDR6, GDDR7-Next (la base de la futura GDDR8), 3D DRAM, PCIe 7.0 en SSD, UFS 6.0 en móviles y NAND 4D con más de 400 capas.

Por el camino, emergen dos conceptos clave que atraviesan todas las familias de producto:

- AI-D (AI-DRAM): optimización, ruptura del muro de memoria y expansión a nuevos segmentos con CXL, PIM (procesamiento en memoria) y formatos como MRDIMM o SOCAMM2.

- AI-N (AI-NAND/Storage Next): SSD y memorias conscientes de la carga de IA, priorizando rendimiento, ancho de banda o densidad según el caso.

A continuación, las piezas del puzle y por qué importan.

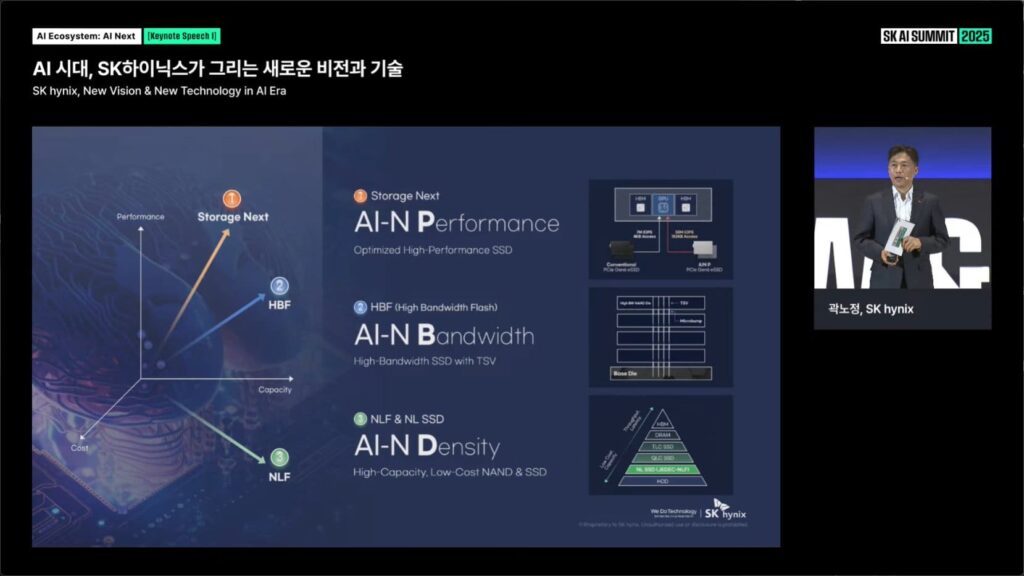

AI-N: tres “perfiles” de almacenamiento para la era IA

En la apertura de la ponencia (“New Vision & New Technology in AI Era”) SK hynix agrupó el almacenamiento del mañana en tres perfiles, todos bajo el paraguas AI-N:

- AI-N Performance (Storage Next): SSD optimizados para alto rendimiento. La compañía mostró un diagrama con rutas de acceso PCIe Gen6 eSSD y una jerarquía en la que el SSD se integra en un tejido de baja latencia junto a CPU, GPU, HBM y NIC. La idea: minimizar cuellos de E/S en workloads token-intensivos y de ventanas de contexto crecientes.

- AI-N Bandwidth (HBF – High Bandwidth Flash): un SSD de alto ancho de banda con TSV. El esquema técnico refleja TSV y microbumps sobre un base die, uniendo matrices de flash con interconexiones verticales para elevar el caudal frente a un eSSD convencional. El objetivo es acercarse —con costes de NAND— a los ritmos que piden entrenamiento e inferencia masivos.

- AI-N Density (NLF & NL SSD): NAND de muy alta capacidad y SSD de bajo coste para almacenamiento masivo. En la pirámide de niveles (HDD→NL SSD→QLC/TLC SSD→DRAM→HBM), esta categoría empuja la capacidad hacia arriba con coste por bit reducido, para alimentar data lakes y repositorios de datasets que crecen sin freno.

Traducción práctica: la compañía no ve un único “SSD de IA”, sino familias especializadas —rendimiento, ancho de banda o densidad— que se combinarán en los centros de datos AI-native.

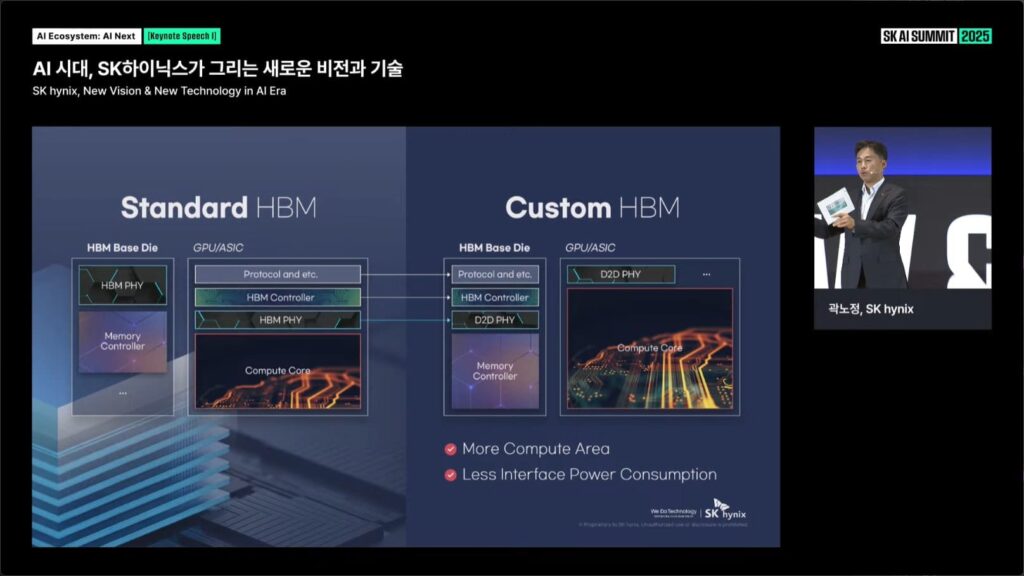

HBM estándar vs HBM “a medida”: mover las piezas para ahorrar vatios y ganar área de cómputo

Otro bloque clave de la presentación opone HBM estándar con HBM personalizada. En el diseño convencional, gran parte de los bloques de interfaz (PHY/Controladores) se reparten entre el HBM base die y el SoC/GPU. La propuesta “Custom HBM” reubica funciones:

- En el HBM base die se integran HBM Controller y un D2D PHY (die-to-die).

- En el SoC/GPU, el camino hacia HBM se reduce a un D2D PHY más ligero.

El resultado, según SK hynix: más área disponible para núcleos de cómputo en el chip anfitrión y menor consumo en las interfaces. Es una pista de hacia dónde empuja el mercado: memoria y cómputo seguirán co-diseñándose (DTCO→STCO), especialmente en aceleradores de IA.

AI-D: optimización hoy, ruptura del muro de memoria mañana

Bajo la marca AI-D (AI-DRAM), SK hynix estructura su estrategia de DRAM en tres ejes:

- Optimization (Lower TCO in Datacenter)

- MRDIMM, SOCAMM2 y LPDDR5R para reducir coste total y consumo en racks de cómputo. MRDIMM apunta a mayor ancho de banda por módulo y SOCAMM2 a densidad en factores compactos.

- Breakthrough (Beyond the Memory Wall)

- CXL-CMM (memoria poolable y coherente vía Compute Express Link), LPDDR6-PIM (procesamiento en memoria) y GDDR AiM (aceleración in-memory). La meta es trasladar cómputo (reduce, search, scatter/gather) al lado de los datos, aliviando la presión sobre buses y controladores.

- Expansion (From Datacenter to Everywhere)

- DRAM grado industrial/automoción (LPDDR/HBM) y LPDDR5X/LPDDR6 en dispositivos y edge, para que la IA salga del centro de datos sin sacrificar fiabilidad.

El calendario: 2026–2028 (despliegue) y 2029–2031 (nueva ola)

La diapositiva final resume la hoja de ruta en cuatro líneas verticales (HBM, DRAM convencional, DRAM AI-D, NAND). Estos son los hitos visibles:

2026–2028

- HBM (estándar): HBM4 16-Hi; HBM4E en 8/12/16-Hi.

- HBM (custom): Custom HBM4E para clientes de IA/supercomputación.

- DRAM convencional (estándar): LPDDR6 como nuevo estándar en móviles/portátiles.

- AI-D: LPDDR5X en SOCAMM2, MRDIMM Gen2, LPDDR5R; 2.ª Gen CXL y primeros LPDDR6-PIM.

- NAND (estándar): PCIe Gen5 eSSD (con capacidades objetivo que en roadmaps públicos llegan a 200+ TB en QLC), paso a PCIe Gen6 eSSD/cSSD y UFS 5.0 en móviles.

- NAND (AI-N): arranque de AI-N D (familia orientada a densidad y gestión predictiva de datos).

Qué significa: un despliegue masivo de HBM4/4E para entrenar e inferir modelos frontera, móviles con LPDDR6, y SSD PCIe 6.0 como base en nuevos racks. Empieza la convergencia CXL y aparecen primeros PIM comerciales.

2029–2031

- HBM (estándar): HBM5 y HBM5E.

- HBM (custom): variantes a medida de HBM5/HBM5E.

- DRAM convencional (estándar): GDDR7-Next (base de la futura GDDR8), DDR6 y 3D DRAM.

- AI-D: LPDDR6 sobre SOCAMM2 (expansión), 3.ª Gen CXL y PIM-Next (siguiente generación de cómputo en memoria).

- NAND (estándar): PCIe Gen7 eSSD/cSSD, UFS 6.0 y NAND 4D de 400+ capas.

- NAND (AI-N): AI-N P (Storage Next) y AI-N B (HBF) maduran, llevando ancho de banda y optimización por IA a primera línea.

Qué significa: una nueva ola que empareja HBM5 con aceleradores de próxima generación y lleva DDR6/GDDR7-Next al PC y al gaming. En almacenamiento, PCIe 7.0 en datacenter, UFS 6.0 en móviles y NAND 4D que rompe la barrera de 400 capas.

Implicaciones: IA, gaming, móviles y edge

- Entrenamiento e inferencia frontera: HBM4E→HBM5 y HBF (flash con TSV) ensancharán el tubo de datos desde el SSD hasta la GPU/ASIC, reduciendo cuellos en pipelines token-intensivos y en contextos largos.

- PC y gaming: GDDR7-Next y DDR6 empujarán ancho de banda y latencia; la mención de 3D DRAM sugiere apilados verticales para densidades superiores.

- Móviles y edge: LPDDR6 como base, UFS 6.0 en la segunda mitad de la década y LPDDR6-PIM para inferencia local con menor consumo; aplicaciones de automoción y industria con DRAM “grado” específico.

- Arquitecturas memory-centric: CXL (Gen2→Gen3) habilita pools de memoria compartida y expansión desacoplada; PIM y AiM (accelerated-in-memory) trasladan operaciones cercanas al dato, clave para reducir p99 de latencias.

- Sostenibilidad: aunque no hubo cifras de PUE/WUE en las diapositivas, el desplazamiento a HBM5/HBM5E y HBM custom apunta a recortar vatios en interfaces y a mejor área de cómputo por die, dos factores críticos en el consumo de los racks de IA.

Qué hace distinto este roadmap

- Memoria como sistema, no como componente: custom HBM, CXL, PIM y AiM indican co-diseño con CPU/GPU/ASIC.

- Almacenamiento “consciente” de IA: AI-N separa perfiles (Performance/Bandwidth/Density) y anticipa flash de alto ancho de banda (HBF) con TSV.

- Calendario largo y coherente: la visión llega a 2031 y enlaza familias (HBM, DRAM, NAND) con puntos de cruce claros entre etapas.

Si SK hynix cumple, no solo acompañará a la IA: podría marcar el ritmo y condicionar diseños de aceleradores, servidores y dispositivos finales durante la próxima década.

Qué observar a partir de 2026

- HBM4E 16-Hi en aceleradores comerciales y la adopción de HBM custom (ahorro de potencia/área real).

- Latencias y throughput de HBF frente a eSSD PCIe 6.0 convencionales.

- CXL de 2.ª generación en producción (latencia agregada, software stack y orquestación).

- Primeras demos de LPDDR6-PIM y GDDR AiM en casos reales (filtrado, reduce, búsquedas).

- Evolución de densidad en NAND 4D hacia las 400+ capas anunciadas para 2029–2031.

Preguntas frecuentes (FAQ)

¿Cuándo llegará la HBM5 al mercado según SK hynix?

En la segunda etapa del roadmap, entre 2029 y 2031. SK hynix contempla HBM5 y HBM5E tanto en versiones estándar como custom, destinadas a aceleradores de IA y GPU de próxima generación.

¿Qué es HBF (High Bandwidth Flash) y en qué se diferencia de un SSD convencional?

HBF es un concepto de flash con alto ancho de banda que emplea TSV y microbumps para aumentar el caudal efectivo frente a un eSSD PCIe convencional. No sustituye a la HBM; acerca el almacenamiento a los ritmos que demandan entrenamiento e inferencia a gran escala.

¿Qué tecnologías de DRAM veremos en 2026–2028 y cuáles a partir de 2029?

Entre 2026 y 2028: LPDDR6 como estándar, MRDIMM Gen2, SOCAMM2, CXL Gen2 y LPDDR6-PIM inicial.

De 2029 a 2031: DDR6, GDDR7-Next (base de GDDR8), 3D DRAM, CXL Gen3 y PIM-Next.

¿Qué adelanta SK hynix en almacenamiento móvil y de datacenter más allá de 2028?

Para datacenter: PCIe Gen7 eSSD/cSSD y NAND 4D de 400+ capas en 2029–2031.

Para móvil: UFS 6.0 y continuidad de LPDDR6 como estándar de memoria, con PIM y variantes de IA-N enfocadas a densidad y eficiencia.

Fuentes

- SK AI Summit 2025 – Presentación “AI Ecosystem: AI Next | SK hynix, New Vision & New Technology in AI Era” (diapositivas de keynote con gráficos AI-N, AI-D, comparativa HBM estándar vs HBM custom y roadmap 2026–2031).

- Material visual oficial de SK hynix mostrado durante la conferencia (capturas facilitadas).

SK Hynix Memory in AI, and new product roadmap pic.twitter.com/x2zqdAo1JC

— 포시포시 (@harukaze5719) November 3, 2025