La memoria se ha convertido en uno de los grandes cuellos de botella de la Inteligencia Artificial. Durante años, el foco ha estado puesto en las GPU, los aceleradores y los grandes clústeres de cálculo, pero el rendimiento real de muchos sistemas depende cada vez más de la velocidad con la que pueden mover datos. Ahí es donde HBM se ha hecho casi imprescindible para entrenar y ejecutar modelos avanzados. Y ahí es también donde Intel y SAIMEMORY, filial de SoftBank, quieren abrir una vía alternativa con ZAM, una nueva arquitectura de memoria 3D de alto ancho de banda.

ZAM, siglas de Z-Angle Memory, no es todavía un producto comercial ni una memoria lista para llegar a los servidores de los hiperescalares. Es una tecnología en desarrollo, con ambiciones claras: ofrecer más ancho de banda, más densidad y menor consumo que las soluciones actuales basadas en HBM. La presentación técnica prevista en el VLSI Symposium 2026 ha añadido datos suficientes para que el sector empiece a mirarla con atención, aunque también con prudencia. Una cosa es demostrar una arquitectura avanzada en laboratorio y otra muy distinta producirla en volumen, con costes competitivos y fiabilidad industrial.

Qué propone ZAM frente a la memoria HBM

HBM domina ahora el segmento de memoria de alto rendimiento porque permite colocar pilas de DRAM muy cerca del procesador o acelerador, con una interfaz extremadamente ancha. Es una solución cara y compleja, pero encaja muy bien con las necesidades de la Inteligencia Artificial y la computación de alto rendimiento. El estándar HBM4, ya publicado, eleva la referencia hasta 2 TB/s por pila y hasta 64 GB de capacidad por stack en sus configuraciones máximas.

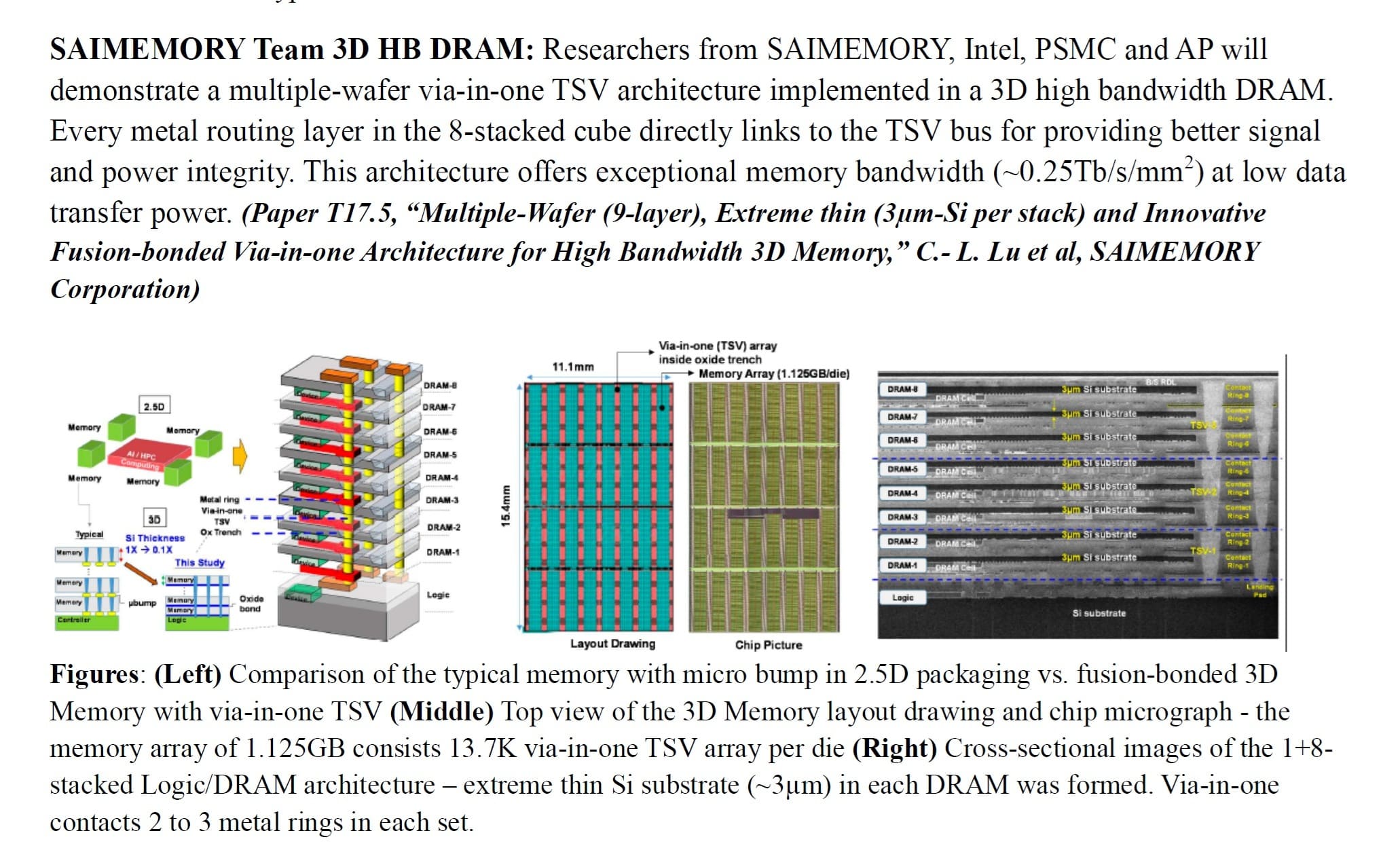

La propuesta de ZAM intenta atacar el mismo problema desde otra arquitectura. Según los materiales técnicos del VLSI Symposium, investigadores de SAIMEMORY, Intel, PSMC y AP Memory presentarán una memoria DRAM 3D de alto ancho de banda basada en una estructura de múltiples obleas, con una arquitectura via-in-one TSV y unión por fusión. El diseño descrito conecta cada capa metálica de enrutado del cubo apilado de ocho capas directamente al bus TSV, con el objetivo de mejorar la integridad de señal y de alimentación.

El dato más llamativo es la densidad de ancho de banda: alrededor de 0,25 Tb/s/mm² con bajo consumo durante la transferencia de datos. En la documentación visual de la ponencia también se aprecia una comparación entre el empaquetado 2.5D habitual con microbumps y una memoria 3D unida por fusión con via-in-one TSV. El esquema muestra una arquitectura 1+8, con una lógica base y ocho capas DRAM, sustratos de silicio extremadamente finos de unos 3 µm por capa y una matriz de 13.700 TSV por die.

Las cifras que circulan alrededor de ZAM apuntan a un rendimiento que podría duplicar el ancho de banda de HBM4 en determinadas configuraciones. Conviene leer esa comparación con cuidado. El dato consolidado en el resumen técnico es la densidad de ancho de banda de la arquitectura, no una especificación comercial cerrada de producto. Para que ZAM pueda compararse de forma justa con HBM4 o HBM4E habrá que conocer capacidad final, rendimiento sostenido, consumo real, coste de fabricación, rendimiento por oblea y comportamiento térmico en aceleradores completos.

| Tecnología | Estado | Ancho de banda citado | Capacidad citada | Principal reto |

|---|---|---|---|---|

| HBM4 | Estándar publicado | Hasta 2 TB/s por stack | Hasta 64 GB por stack | Coste, suministro y complejidad de empaquetado |

| ZAM | Desarrollo y demostración técnica | ~0,25 Tb/s/mm² de densidad | Datos aún no cerrados como producto | Producción en volumen y validación en sistemas reales |

Una apuesta industrial, no solo una ponencia técnica

La colaboración entre Intel y SAIMEMORY no aparece de la nada. SoftBank anunció en febrero de 2026 que su filial había firmado un acuerdo con Intel para avanzar en la comercialización de ZAM como tecnología de nueva generación orientada a alta capacidad, alto ancho de banda y bajo consumo. El plan comunicado por la compañía habla de prototipos durante el año fiscal que finaliza el 31 de marzo de 2028 y de una posible comercialización en el año fiscal 2029.

Ese calendario sitúa a ZAM en una carrera de medio plazo. No compite con las HBM3E actuales ni con las primeras implementaciones de HBM4 que empezarán a llegar antes. Su ventana natural estaría más cerca de la siguiente fase de la infraestructura de Inteligencia Artificial, cuando los sistemas no solo necesiten más cálculo, sino también más memoria por acelerador y menos energía por bit transferido.

Intel aporta en esta historia una parte importante de experiencia en empaquetado avanzado, interconexión y tecnologías de unión de DRAM. SoftBank, por su parte, busca reforzar su posición en infraestructura de Inteligencia Artificial desde Japón, no solo como inversor, sino también como impulsor de tecnologías base. SAIMEMORY se creó en diciembre de 2024 para trabajar en memorias de nueva generación, y el proyecto encaja con la estrategia japonesa de recuperar peso en semiconductores avanzados.

El componente geopolítico tampoco es menor. La cadena de suministro de HBM está muy concentrada y depende de pocos fabricantes, principalmente SK hynix, Samsung y Micron. Para compañías que están invirtiendo miles de millones en centros de datos de Inteligencia Artificial, cualquier alternativa que pueda reducir dependencia, consumo o coste merece atención. ZAM no tendría que destruir el mercado de HBM para ser relevante. Bastaría con convertirse en una opción viable en ciertos diseños de aceleradores, servidores o sistemas HPC.

El gran examen será fabricar ZAM a escala

La parte más atractiva de ZAM está en su arquitectura vertical. Al reducir distancias internas y usar vías TSV integradas de forma más directa, la tecnología promete mover datos con menos energía y mejorar la disipación térmica respecto a ciertas limitaciones de las pilas HBM convencionales. Esa promesa resulta especialmente importante en centros de datos donde el consumo eléctrico, la refrigeración y la densidad por rack ya condicionan el despliegue de nuevos clústeres.

Pero la historia de los semiconductores está llena de tecnologías brillantes que tardaron años en salir del laboratorio o nunca alcanzaron costes razonables. El empaquetado 3D, las uniones por fusión, el adelgazamiento extremo de obleas y la validación de miles de interconexiones por capa no son tareas menores. La fiabilidad a largo plazo, la reparación de defectos, el rendimiento de fabricación y la compatibilidad con controladores y aceleradores reales serán tan importantes como el ancho de banda máximo.

También hay debate sobre el posible uso de nodos de fabricación maduros en la parte DRAM, especialmente por la participación de PSMC. Algunas interpretaciones apuntan a que ZAM podría apoyarse en procesos menos avanzados que los de las memorias HBM más recientes, compensando esa diferencia con arquitectura y empaquetado. Por ahora ese punto debe tratarse como especulación: el resumen técnico público confirma la arquitectura, los TSV, el apilado y las métricas de ancho de banda por superficie, pero no basta para cerrar una lectura industrial completa.

La lectura más realista es que ZAM abre una nueva vía en el segmento de memoria para Inteligencia Artificial, pero aún no destrona a HBM. HBM ya tiene estándar, proveedores, clientes, diseños en marcha y una presencia clara en las hojas de producto de NVIDIA, AMD, Google, Intel y otros fabricantes de aceleradores. ZAM necesita demostrar que puede pasar de una arquitectura prometedora a un componente fabricable, integrable y competitivo.

Si lo consigue, el efecto puede ser relevante. Más alternativas de memoria de alto ancho de banda aliviarían parte de la presión que sufre el mercado de aceleradores de Inteligencia Artificial, permitirían nuevos diseños de chips y podrían reducir el consumo asociado al movimiento masivo de datos. Si no lo consigue, al menos habrá servido para empujar al sector hacia arquitecturas de memoria más ambiciosas. En ambos casos, el mensaje es claro: la próxima batalla de la Inteligencia Artificial no se librará solo en los núcleos de cálculo, sino en la memoria que los alimenta.

Preguntas frecuentes

¿Qué es ZAM?

ZAM, o Z-Angle Memory, es una tecnología de memoria 3D de nueva generación desarrollada por SAIMEMORY con colaboración de Intel. Está pensada para ofrecer alto ancho de banda, alta capacidad y menor consumo en sistemas de Inteligencia Artificial y computación de alto rendimiento.

¿ZAM sustituirá a HBM?

Todavía es pronto para afirmarlo. ZAM apunta a competir con HBM en el futuro, pero HBM ya está estandarizada, tiene fabricantes consolidados y está integrada en aceleradores actuales y próximos. ZAM debe demostrar fabricación a escala y uso real en sistemas comerciales.

¿Cuándo podría llegar ZAM al mercado?

SoftBank y SAIMEMORY han hablado de prototipos durante el año fiscal 2027, que termina el 31 de marzo de 2028, y de una posible comercialización en el año fiscal 2029. Ese calendario puede cambiar según avance la validación técnica e industrial.

¿Por qué importa esta tecnología para la Inteligencia Artificial?

Los modelos avanzados necesitan mover enormes volúmenes de datos entre memoria y aceleradores. Una memoria con más ancho de banda y menor consumo puede mejorar el rendimiento, reducir costes energéticos y permitir sistemas más densos en centros de datos.

"Microelectronic Assemblies including Stacked Dies Coupled by A Through Dielectric Via", Stephen Morein (CTO, SAIMEMORY, Aug 2025 –), …, Prashant Majhi, Intel (Jun 2022) https://t.co/hh6alJx32o

— OGAWA, Tadashi (@ogawa_tter) May 2, 2026

<= VLSI 2026 https://t.co/KnYRmN9PSp

ZAM、4月22日 https://t.co/sftnfz2DWD

38億円🤔 pic.twitter.com/PDYLAnGTuI