Durante años, la batalla de los semiconductores se contó casi siempre desde la óptica del nodo, la litografía o el diseñador del chip. Pero la fiebre de la Inteligencia Artificial ha desplazado parte de esa conversación hacia otro terreno mucho menos vistoso para el gran público y, sin embargo, decisivo: el empaquetado avanzado. Ahí es donde TSMC ha logrado convertir CoWoS en una pieza central del ecosistema de aceleradores para IA, mientras Intel intenta abrirse paso con EMIB y su evolución EMIB-T como una opción cada vez más seria dentro de su negocio de foundry.

La fotografía oficial deja una idea bastante clara. TSMC define CoWoS como una tecnología pensada para computación de muy alto rendimiento, con integración de chiplets lógicos y memoria HBM, y la vincula de forma directa a aplicaciones de Inteligencia Artificial y supercomputación. Intel, por su parte, presenta EMIB como un sistema 2.5D para unir varios chips complejos dentro de un mismo encapsulado, también con soporte para configuraciones de lógica con HBM, y subraya que se trata de una tecnología ya probada en producción desde 2017. EMIB-T añade TSVs al puente para reforzar la integración y facilitar el encaje de diseños procedentes de otros esquemas de empaquetado.

Ese contraste ayuda a entender por qué el debate ya no gira solo en torno a quién fabrica mejor el chip, sino a quién puede integrarlo mejor, más rápido y con una cadena de suministro menos frágil. La propia NIST, a través del programa estadounidense CHIPS National Advanced Packaging Manufacturing Program, lo resume sin rodeos: las inversiones en semiconductores no tendrán éxito sin inversiones en empaquetado avanzado. No es un matiz menor. Es una admisión oficial de que el cuello de botella no está solo en la oblea, sino también en cómo se ensamblan, conectan, alimentan y validan esos chips cada vez más complejos.

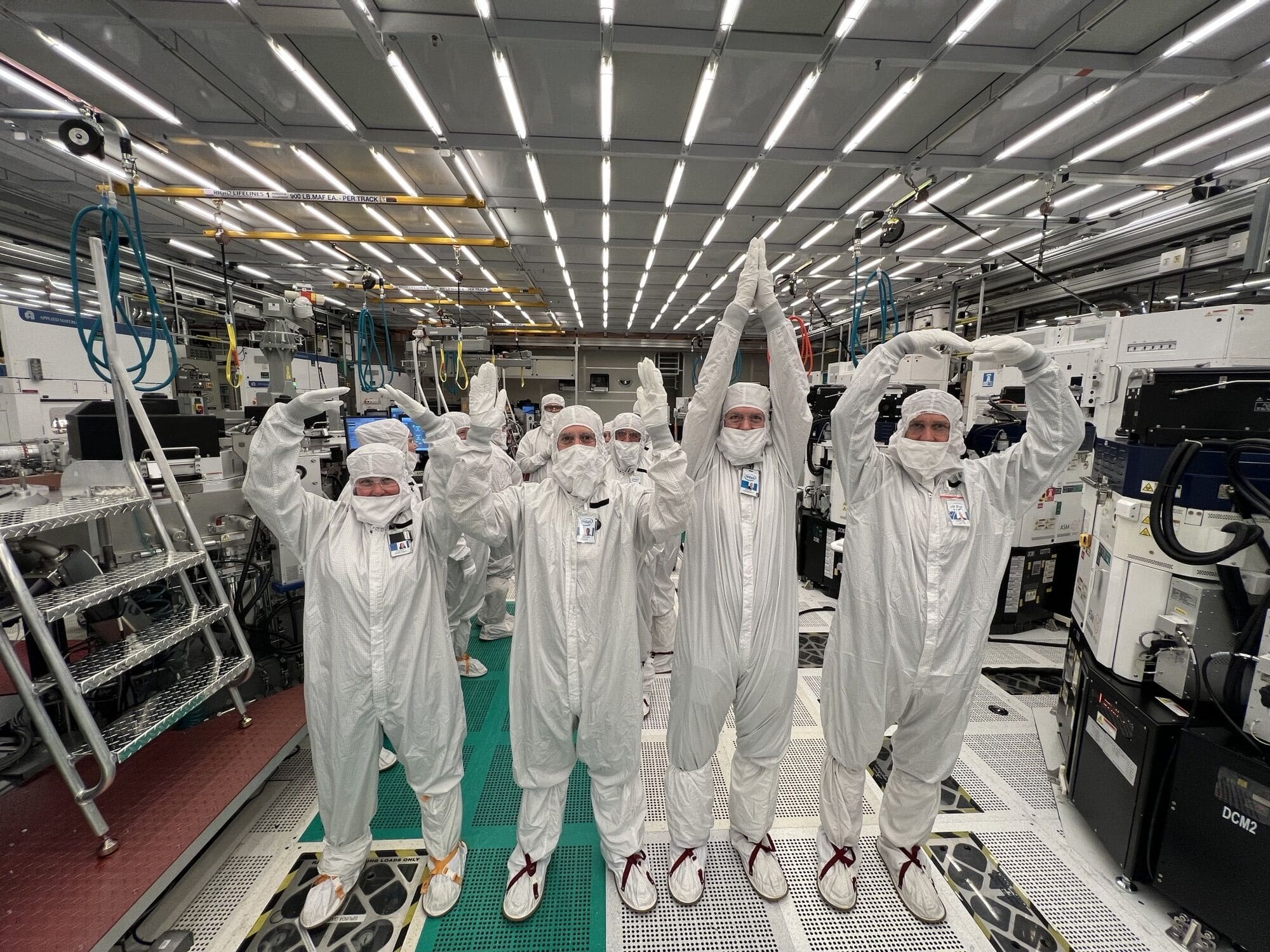

Intel quiere aprovechar precisamente esa ventana. La compañía lleva tiempo intentando convencer al mercado de que su oferta no es solo una respuesta técnica, sino también una respuesta industrial y geográfica. En enero de 2024 abrió Fab 9 en Rio Rancho, Nuevo México, dentro de una inversión de 3.500 millones de dólares, y la presentó como parte de su primer emplazamiento operativo para producción masiva de empaquetado avanzado 3D. En ese momento, Intel llegó a describir la instalación como la única fábrica en Estados Unidos que producía a escala sus soluciones de empaquetado avanzado más punteras. A efectos de relato industrial, era una forma de decir que no solo tenía tecnología, sino también capacidad doméstica real.

El cuello de botella ya no está solo en fabricar el chip

La presión del mercado ayuda a explicar por qué este asunto ha ganado tanta importancia. La IA generativa ha disparado la demanda de chips de alto rendimiento, pero esa demanda no depende únicamente de disponer de más obleas avanzadas. También exige interconexiones de muy alta densidad, memorias HBM, disipación térmica, integridad de señal y consumo eléctrico controlado dentro de encapsulados cada vez más complejos. En ese contexto, el empaquetado avanzado deja de ser la última fase del proceso y pasa a convertirse en una parte estratégica del producto.

TSMC sigue partiendo con ventaja en ese terreno. Su plataforma 3DFabric agrupa tecnologías como CoWoS, SoIC e InFO, y la propia compañía ha colocado CoWoS en el centro de sus propuestas para IA y HPC. Además, lejos de quedarse quieta, anunció en marzo de 2025 una ampliación de su inversión en Estados Unidos hasta 165.000 millones de dólares, incluyendo dos instalaciones de empaquetado avanzado en Arizona. El movimiento es importante porque rebaja una lectura demasiado simple del mercado: Intel no compite sola como “respuesta americana”, ya que TSMC también está llevando parte de esa capacidad al suelo estadounidense.

Aun así, Intel sí tiene una baza evidente. Mientras TSMC construye esa expansión, Intel ya dispone de una base industrial de empaquetado avanzado en Estados Unidos y la usa como argumento comercial para atraer a clientes que buscan mayor resiliencia en la cadena de suministro. En semiconductores, reducir desplazamientos, simplificar ensamblaje y evitar dependencias innecesarias ya no es solo una cuestión logística: es una cuestión de coste, plazo y riesgo geopolítico. Y eso vale especialmente para compañías fabless que quieren fabricar en EE. UU. o, al menos, tener una parte relevante de su cadena más cerca.

Intel juega la carta de la capacidad local y la flexibilidad

La propuesta técnica de EMIB también tiene sentido dentro de esa estrategia. Intel lo describe como una forma eficiente y rentable de conectar varios dies complejos mediante un puente de silicio embebido en el sustrato del encapsulado, sin recurrir necesariamente a un gran interposer completo como en otros planteamientos 2.5D. Sobre el papel, eso puede aportar ventajas de coste, flexibilidad de diseño y simplificación del ensamblaje en determinados tipos de producto. EMIB-T, además, incorpora TSVs en el puente, una evolución con la que Intel quiere reforzar el suministro de energía y la interconexión entre chips en diseños de nueva generación orientados a IA.

Ese matiz es importante porque no todos los productos necesitan exactamente lo mismo. CoWoS ha brillado sobre todo en configuraciones donde la prioridad absoluta pasa por integrar grandes cantidades de HBM y maximizar el ancho de banda para aceleradores muy exigentes. EMIB, en cambio, puede resultar especialmente atractivo en proyectos donde además de rendimiento importan la escalabilidad física, el coste y la modularidad del diseño. En la práctica, no todo apunta a una sustitución total de una tecnología por otra, sino a una convivencia en la que cada enfoque intente ganar terreno allí donde mejor encaje.

Lo que sí parece claro es que Intel quiere que EMIB deje de verse como una tecnología interesante pero secundaria y pase a considerarse una pieza con peso propio dentro del nuevo tablero de la IA. Sus mensajes más recientes sobre foundry, packaging y sistemas para la era de la IA van precisamente en esa dirección: presentar EMIB-T no como una curiosidad técnica, sino como una herramienta industrial lista para diseños grandes, heterogéneos y con necesidades energéticas muy exigentes.

Dicho esto, conviene separar con cuidado la parte verificable del ruido de mercado. Las fuentes oficiales consultadas permiten afirmar que Intel cuenta con una oferta de empaquetado avanzado madura, que EMIB está en producción desde hace años, que EMIB-T amplía esa propuesta y que la compañía dispone de capacidad industrial en Estados Unidos. También permiten afirmar que TSMC sigue situando CoWoS como referencia para IA y que está ampliando su presencia de empaquetado avanzado en Arizona. Lo que no debería darse por cerrado sin anuncios concretos son las listas de clientes, los contratos multimillonarios o las apuestas de producto atribuidas a terceros en informes no oficiales. En un sector tan sensible, la diferencia entre una expectativa y un pedido firme sigue siendo enorme.

En el fondo, esa es la verdadera lectura de todo este movimiento. El negocio del chip para IA ya no se decide solo en la fábrica que imprime transistores. También se decide en el encapsulado, en la proximidad industrial, en la capacidad de integrar memoria y lógica sin disparar el coste y en la posibilidad de ofrecer a los clientes una cadena de suministro menos expuesta. Ahí TSMC sigue mandando con una ventaja clara, pero Intel ha encontrado en EMIB una forma creíble de meterse en la conversación. Y en un mercado donde el empaquetado avanzado se ha convertido en un cuello de botella estratégico, eso ya no es un detalle menor.

Preguntas frecuentes

¿Qué diferencia hay entre Intel EMIB y TSMC CoWoS en chips para IA?

EMIB usa un puente de silicio embebido en el sustrato para unir varios dies dentro del encapsulado, mientras que CoWoS se apoya en tecnologías de interposer e integración avanzadas muy orientadas a HPC e Inteligencia Artificial con HBM. En términos generales, CoWoS se ha consolidado como referencia en grandes aceleradores de IA, mientras que EMIB busca ganar peso con una propuesta más flexible y con fuerte componente industrial en Estados Unidos.

¿Por qué el empaquetado avanzado es tan importante para la Inteligencia Artificial?

Porque los chips modernos para IA ya no dependen solo del nodo de fabricación. Necesitan integrar varios chiplets, memoria HBM, alimentación eléctrica estable, disipación térmica y conexiones de muy alta densidad. La propia NIST subraya que no habrá una industria competitiva de semiconductores sin una base sólida de empaquetado avanzado.

¿Tiene Intel capacidad de empaquetado avanzado en Estados Unidos?

Sí. Intel abrió Fab 9 en Nuevo México en 2024 y la integró con Fab 11X como su primer emplazamiento operativo de gran volumen para empaquetado avanzado 3D. La compañía lo presentó como una pieza clave para reforzar su cadena de suministro y su oferta industrial doméstica.

¿TSMC también va a hacer empaquetado avanzado en Arizona?

Sí. TSMC anunció en 2025 que ampliará su inversión en Estados Unidos hasta 165.000 millones de dólares, incluyendo dos instalaciones de empaquetado avanzado en Arizona. Eso refuerza la idea de que la competencia por el backend avanzado también se está desplazando al mercado estadounidense.