La carrera por la Inteligencia Artificial ya no se decide solo por quién fabrica más GPUs o quién entrena el modelo más grande. En 2026, el cuello de botella cada vez más evidente está en la memoria: su ancho de banda, su capacidad y, sobre todo, su disponibilidad. En ese escenario, China empieza a enseñar una carta que apunta directamente al dominio de Corea del Sur en memorias avanzadas: YMTC (Yangtze Memory Technologies) trabaja en un concepto llamado High Bandwidth Flash (HBF), una propuesta que busca acercar la NAND 3D al cómputo para cubrir un hueco que la HBM —clave en aceleradores de IA— empieza a dejar al descubierto.

La tesis es sencilla, aunque incómoda para el mercado: HBM (High Bandwidth Memory) ofrece un rendimiento excelente, pero es cara, compleja de empaquetar y limitada en capacidad total cerca de la GPU. Y cuando los modelos crecen, el problema ya no es solo “ir rápido”, sino mantener muchos datos cerca (pesos, estados intermedios, checkpoints, datasets, historiales). Ahí es donde YMTC plantea que la flash podría jugar un papel nuevo: no como SSD “lejano”, sino como memoria apilada y conectada con un ancho de banda mucho mayor que el almacenamiento convencional.

¿Qué es HBF y por qué ahora aparece en la conversación?

HBF, tal y como se está describiendo en el sector, aspira a ser una memoria flash de muy alta capacidad que se integra más cerca del procesador o acelerador, con un diseño de interconexión pensado para mover datos a velocidades superiores a las de un SSD típico. Su promesa no es sustituir a HBM en latencia —sería irrealista—, sino ofrecer más capacidad cerca del cómputo y aliviar la presión sobre el “pool” de memoria más caro del sistema.

El detalle relevante es que no es una idea aislada ni un simple concepto de laboratorio. En paralelo a los movimientos chinos, Sandisk y SK hynix anunciaron un acuerdo para trabajar en la estandarización de una especificación de HBF, describiéndola como una tecnología pensada para cargas de IA (especialmente inferencia) y con una ambición muy concreta: ancho de banda comparable a HBM y entre 8 y 16 veces más capacidad, con un coste “similar” en su objetivo de mercado, además de un calendario que apunta a muestras en 2026 y dispositivos iniciales en 2027. Dicho de otro modo: la industria está, literalmente, intentando “inventar” una nueva capa de memoria para la era de la IA.

El plan chino: YMTC quiere que la NAND deje de ser “solo SSD”

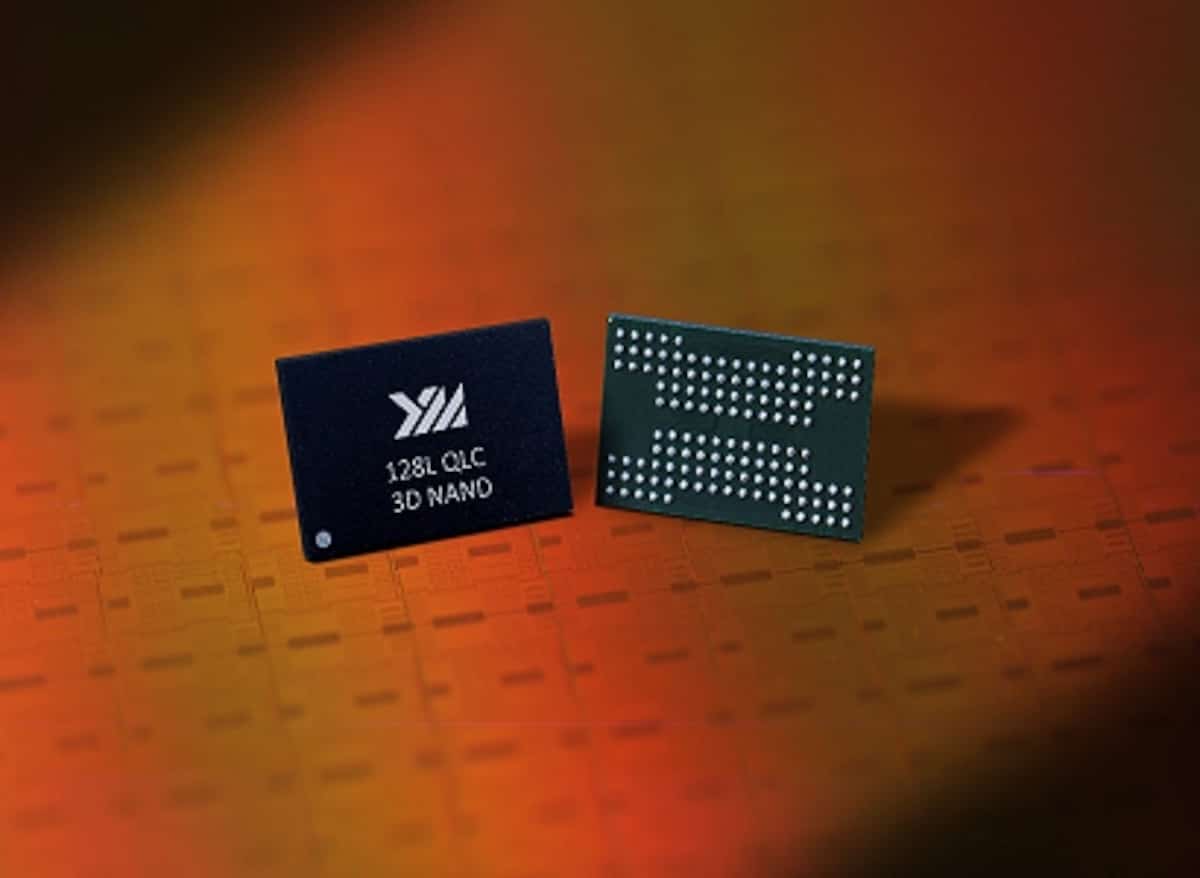

En ese contexto llega el movimiento de YMTC. Según información del mercado tecnológico asiático, la compañía ha divulgado avances en 3D NAND y su intención de desarrollar HBF, apoyándose en la evolución de su arquitectura Xtacking. El enfoque de Xtacking —resumido— consiste en separar la fabricación de la matriz de memoria y la parte lógica/periférica en obleas distintas y unirlas mediante técnicas de bonding, una estrategia que busca mejorar rendimiento y escalabilidad al optimizar cada bloque por separado.

La lectura geoestratégica es evidente: YMTC opera en un entorno condicionado por restricciones tecnológicas y por el objetivo nacional de reducir dependencias en semiconductores. Si Corea del Sur domina HBM y buena parte de la memoria “premium” que alimenta a las GPU de IA, una “memoria alternativa” basada en la fortaleza china en NAND podría ser una vía de escape: más capacidad cerca del cómputo, aunque con compromisos.

HBM vs HBF: la comparación que importa (y el matiz que muchos pasan por alto)

Para entender por qué HBF genera ruido, conviene poner el problema en términos prácticos:

- HBM (DRAM apilada): excelente para alimentar GPUs con datos a gran velocidad y baja latencia. Es lo que permite que un acelerador rinda de verdad. Pero su capacidad por paquete es limitada y su producción depende de una cadena compleja (DRAM avanzada, TSV, packaging 2.5D/3D, interposers…).

- Flash (NAND): barata por GB y escalable en capacidad. Pero su latencia y su naturaleza de almacenamiento la hacen inadecuada para sustituir a DRAM en el “frontline” del cómputo.

HBF intenta posicionarse en medio: no pretende ser la RAM de la GPU, sino un escalón cercano que permita guardar más datos junto al acelerador sin pagar siempre el “impuesto HBM”. En un mundo donde cada iteración de modelos empuja a guardar más checkpoints, más versiones, más resultados y más históricos —por reproducibilidad, auditoría o cumplimiento—, la presión ya no es solo de cálculo: es de memoria y almacenamiento cercanos.

El matiz técnico es el que separa la promesa del titular fácil: si HBF se usa para lo que no toca (datos que exigen latencia tipo DRAM), será un fracaso. Si se usa como memoria de gran capacidad para inferencia, staging, cacheado de ciertos activos, o tiers intermedios, puede tener sentido económico y operativo.

¿Por qué este movimiento amenaza a Samsung y SK hynix… aunque HBF no sea HBM?

Porque el poder no está solo en vender HBM: está en controlar el estándar de facto de memoria para IA. Si el mercado acepta una arquitectura donde parte del “problema de capacidad” se resuelve con flash apilada, la discusión se abre: ¿cuánta HBM hace falta realmente por nodo para ciertos escenarios? ¿qué parte del presupuesto se puede desplazar a otra capa?

Y ahí YMTC ve una oportunidad: China puede no liderar HBM de última generación, pero sí puede intentar liderar un “nuevo carril” con NAND, bonding y empaquetado avanzado. Además, si se consolida un ecosistema HBF —y el hecho de que Sandisk y SK hynix hablen ya de estandarización indica que se está intentando—, el tablero de proveedores se reordena.

Lo que falta por demostrar: fiabilidad, software y una pregunta brutal

Aun así, conviene rebajar la épica: HBF es una apuesta con retos serios. La flash tiene desgaste, necesita gestión compleja y su rendimiento real depende de controladores, firmware y, sobre todo, de cómo el software de IA se adapte a una jerarquía de memoria más rica. El éxito no será “hacer un cartucho más grande”, sino construir un sistema donde compense mover datos a ese nuevo escalón sin romper latencias ni eficiencia energética.

La pregunta que sobrevuela todo es tan simple como determinante: ¿HBF reducirá el número de GPUs necesarias para una tarea, o solo permitirá hacer más con las mismas? Si la respuesta es lo segundo, el mercado lo adoptará igual, porque el incentivo en IA es claro: escalar.

Preguntas frecuentes

¿Qué diferencia hay entre HBM y HBF en centros de datos de IA?

HBM es memoria DRAM apilada con latencia muy baja y ancho de banda altísimo para alimentar a la GPU. HBF busca aportar mucha más capacidad usando flash, con un objetivo de ancho de banda elevado, pero sin sustituir a HBM en tareas sensibles a latencia.

¿Para qué serviría la High Bandwidth Flash en inferencia de modelos grandes?

Principalmente para aportar una “capa cercana” de gran capacidad que ayude a manejar modelos, históricos y datos que no necesitan estar siempre en la memoria más rápida, mejorando costes y escalabilidad en ciertos despliegues.

¿HBF puede reducir la dependencia de HBM a corto plazo (2026–2027)?

Puede aliviar parte de la presión en escenarios donde la limitación sea la capacidad cercana al cómputo, pero no elimina la necesidad de HBM para rendimiento máximo. El impacto real dependerá de productos disponibles y adopción por el software.

¿Qué riesgos tiene acercar memoria flash a una GPU o acelerador de IA?

El mayor reto es la combinación de latencia, gestión del desgaste, fiabilidad y la necesidad de un stack de software que aproveche bien una jerarquía de memoria más compleja sin penalizar rendimiento.

Fuentes:

- Sandisk

- Future Memory Storage

- Tom’s Hardware

- DIGITIMES Asia.