La ambición de la Casa Blanca de equilibrar al 50 % la fabricación de semiconductores destinados al mercado estadounidense entre Estados Unidos y Taiwán tropieza con un obstáculo estructural: EE. UU. no dispone aún de una cadena de suministro doméstica madura —desde materiales críticos hasta packaging avanzado— capaz de sostener, por sí sola, una cuota tan agresiva en los nodos punteros (EUV) que hoy alimentan IA, 5G, móviles y centros de datos.

La propuesta, defendida en público por el secretario de Comercio Howard Lutnick, pretende que la mitad de los chips que consumen las empresas y los ciudadanos estadounidenses se fabriquen en plantas situadas en territorio nacional. El razonamiento político-estratégico es transparente: reducir la dependencia de la isla en un escenario de crisis y reforzar la capacidad de disuasión y defensa de Taiwán sin que el suministro de silicio actúe como rehén. En paralelo, la Administración vincula esa ambición a compromisos de seguridad y presiona con aranceles del 100 % a semiconductores importados, con exenciones para quienes inviertan en fábricas en EE. UU. (como TSMC o Samsung).

Un objetivo sin definición operativa

El plan, sin embargo, carece de una definición trabajable, según funcionarios y analistas en Taipéi. ¿“50/50” de qué? ¿Solo nodos avanzados o también nodos maduros? ¿Se incluye el packaging avanzado (2.5D/3D), la memoria o solo lógica? ¿Abarca todo lo que se consume en EE. UU. o un subconjunto gubernamental/estratégico? Sin ese marco, no hay métrica sobre la que discutir viabilidad, costes, plazos o incentivos.

El analista Ming-Chi Kuo lo condensa así: sin acotar familias de producto, niveles de tecnología y destinatarios, el “50/50” esloganiza, pero no planifica. De ahí que Cheng Li-Chun, viceprimer ministro taiwanés, niegue que se hayan celebrado negociaciones formales en esos términos.

El estado real de la industria estadounidense

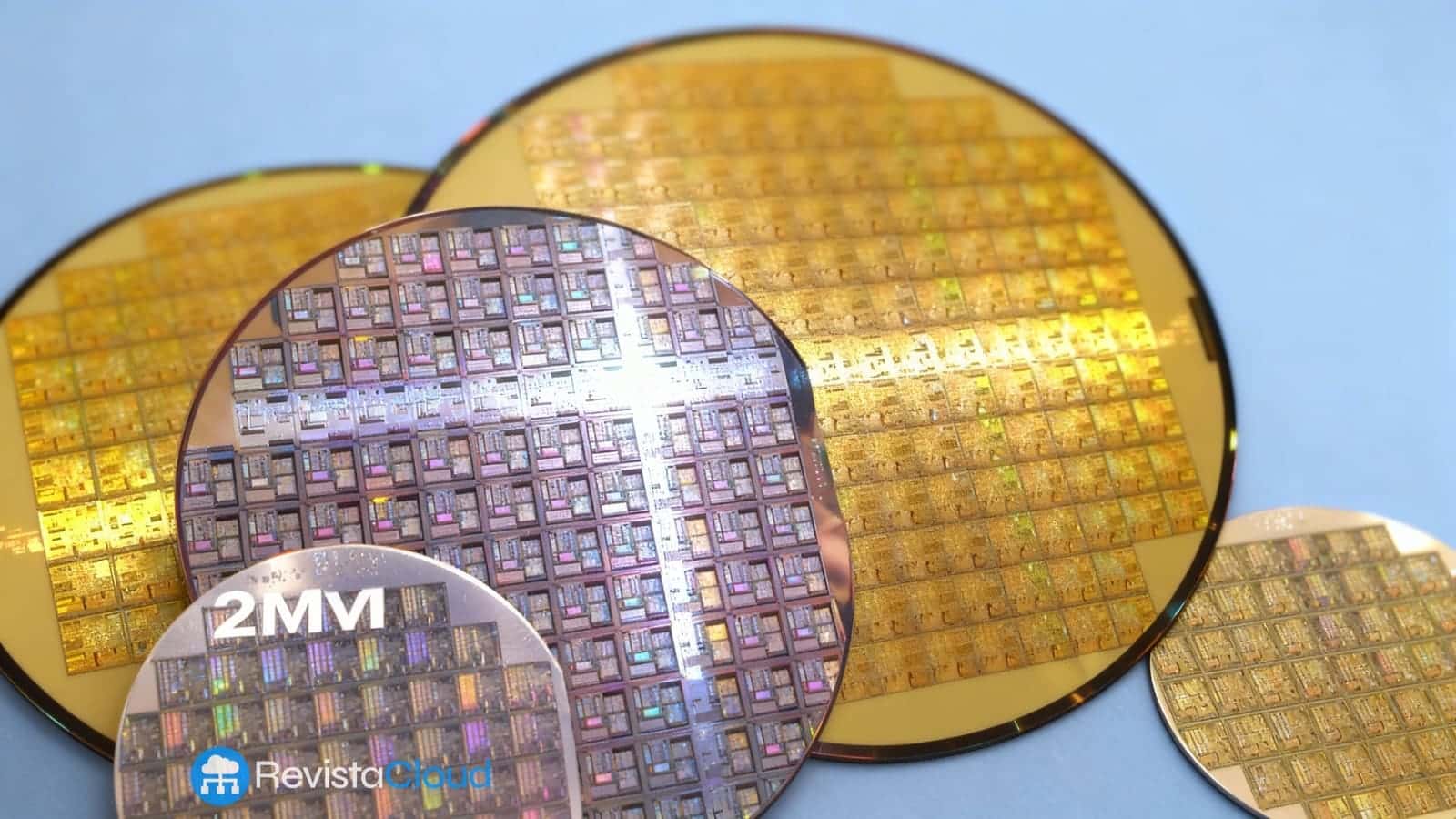

Conviene separar volumen de vanguardia. Estados Unidos ya fabrica una gran cantidad de chips en nodos maduros (automoción, potencia, industrial) con Analog Devices, Texas Instruments, GlobalFoundries, onsemi o SkyWater; en unidades y facturación suponen la mayor parte del mercado. Además, Intel produce lógica avanzada en territorio nacional, y TSMC y Samsung amplían sus fabs en Arizona y Texas.

El cuello de botella, no obstante, reside en los nodos EUV de vanguardia (N5/N4/N3 hoy; N2/A16 mañana) y en el packaging avanzado (CoWoS, HBM con interposer, hybrid bonding). Ahí Taiwán —léase TSMC— concentra ≈ 90 % de la producción mundial y marca la pauta. Mover el 50 % de todo lo que consumen las empresas estadounidenses a fábricas en suelo americano mezcla categorías y desenfoca el verdadero reto: autonomía en leading-edge y ecosistema local para soportarla.

TSMC en Arizona: aceleración real, límites tangibles

La expansión de TSMC en Arizona —la mayor inversión extranjera en semiconductores de la historia— avanza más rápido de lo esperado. El plan público suma seis fabs de nodos avanzados, dos plantas de packaging y un centro de I+D. La Fab 21 (fase 1) inició producción en 2024; la fase 2 se ha adelantado a 2S 2027 y subido de nodo (N3→N2 e incluso A16, a petición de Washington). Kuo proyecta que las tres primeras fabs alcancen alta utilización entre 2028 y 2030.

Aun así, con todo en marcha, TSMC-USA representaría ≈ 10–15 % de su capacidad global a 2030, y ≈ 25–30 % cuando las seis fases estén operativas alrededor de 2032. Sumando Intel (Arizona, Ohio) y Samsung (Texas), EE. UU. sí podría cubrir una porción relevante de su demanda de nodos punteros; pero el “50/50” sigue lejos sin una red local de materiales, equipos y packaging a la altura.

La pieza que falta: proveedores y materiales “aguas arriba”

La autonomía no se decreta solo levantando fabs. El suministro de fotoresistentes de ultra alta pureza, underfills, recubrimientos, slurries o química húmeda sigue concentrado en Japón (JSR, Namics, Nagase, etc.). Hoy envían a Arizona para soportar la Fab 21, pero a medida que crezca la capacidad, necesitarían plantas o hubs logísticos en EE. UU. para evitar aranceles y ganar flexibilidad. Montarlas lleva años y, fuera de Asia, el mercado aún es demasiado pequeño para justificar inversiones inmediatas.

La historia se repite en equipos críticos: lithography (Países Bajos), metrología y depósito (Europa y Japón) son irremplazables. Sin localización paralela de materiales y supply chain, trasladar obleas a EE. UU. solo desplaza vulnerabilidades geográficas.

¿Tiene sentido económico?

Desde el coste, producir la mitad de los chips que consume EE. UU. en suelo estadounidense es más caro: incluso con nodos probados (N5/N4), fabricar en Arizona puede suponer ≈ 30 % de sobreprecio frente a Taiwán. Apple, AMD o NVIDIA podrían absorberlo; no todas las compañías pueden. Además, Asia parte con ecosistemas densos (materiales, tool vendors, mantenimiento) que abaratan logística y acortan tiempos de parada. En EE. UU., hay que reconstruir esa red y su aprendizaje.

La lógica cambia si se mira como póliza de seguro. EE. UU. consume 25–33 % de los semiconductores del mundo, fabrica 10–12 % y su capacidad puntera es limitada. Una disrupción en Taiwán —conflicto, bloqueo o terremoto— afectaría cloud (hyperscalers), defensa, sanidad y automoción. En ese prisma, pagar más por parte del silicio es resiliencia; el ROI industrial llega a largo plazo por el efecto arrastre (proveedores, talento, I+D).

Política y símbolos: “reshoring” como narrativa

Para la Administración, la autonomía en chips es símbolo de renacimiento industrial. Los anuncios de Intel, TSMC y Samsung, la cifra de 165.000 millones de dólares atribuida a TSMC y la aceleración de nodos en Arizona alimentan el relato, aunque muchas decisiones nacieran en ciclos políticos previos y su plena capacidad se sitúe a años vista. En paralelo, el “50/50” actúa como mensaje en la mesa de negociación con Taipéi, combinado con la palanca arancelaria.

¿Es posible de verdad un “50/50”?

Aspiracional, sí; viable a corto plazo, no. TSMC fabrica más chips punteros que el resto del mundo junto. Igualar el pulso exigiría múltiples megasites, decenas de miles de herramientas avanzadas y decenas de miles de trabajadores cualificados que EE. UU. hoy no tiene en volumen suficiente. El pipeline laboral para manufactura avanzada sigue corto, alertan los líderes del sector: construir fabs será lento y operarlas, costoso, si no se resuelve la formación.

La ruta práctica pasa por definir qué cubre el “50/50” (por familias y nodos), priorizar leading-edge y packaging, acelerar TSMC/Intel/Samsung en EE. UU. y empujar a proveedores japoneses y europeos a localizar parte de su producción. El objetivo razonable de aquí a principios de los 30: que Arizona, Ohio y Texas cubran una parte sustancial de la demanda doméstica de nodos punteros, mientras se siembra la red de materiales y equipos.

Qué vigilar en los próximos 24–36 meses

- Ramp de TSMC-USA: yields, nodos N2/A16 y capacidad de CoWoS/SoIC en suelo estadounidense.

- Intel Foundry: ejecución en Intel 3/18A y contratos external que confirmen confianza en su roadmap.

- Samsung Texas: calendario y nodos de su segunda ola (y capacidades de advanced packaging).

- Materiales: decisiones de JSR, Namics, Nagase y otros sobre plantas o hubs en EE. UU.

- Mano de obra: programas de formación técnica (community colleges, apprenticeships) y visas para atraer talento.

- Tarifas e incentivos: cómo se aplican los aranceles del 100 % y qué exenciones reciben quienes invierten.

- Memoria: planes de Micron (DRAM) y SK hynix (HBM assembly en EE. UU., ¿dado local?) para evitar que la lógica puntera quede descasada de la memoria.

El fondo del asunto: de “dónde” a “cómo”

El debate útil no es dónde se fabrica el chip, sino cómo se orquesta una cadena de valor completa: materias primas, equipos, fabs, memoria, packaging, logística, talento y clientes ancla. Sin esa visión, el “50/50” es eslogan. Con ella, puede ser un hito parcial (por familias y nodos) de una estrategia más amplia: varios polos verticalmente integrados (EE. UU., Taiwán y aliados) que reduzcan el riesgo sistémico sin destruir la eficiencia de un ecosistema global que, nos guste o no, seguirá siendo interdependiente.

Claves rápidas

- Meta política: elevar la producción doméstica de chips > 40 % antes del fin del mandato actual.

- Herramientas: negociación con Taipéi, aranceles del 100 % (con exenciones por inversión), subvenciones CHIPS Act, presión para acelerar nodos en EE. UU.

- Realidad: EE. UU. fabrica muchos chips (nodos maduros), pero escasea en lógica EUV y packaging. El escollo es el ecosistema, no solo la fab.

- Horizonte: con TSMC/Intel/Samsung desplegadas y proveedores localizados, principios de los 30 podrían cubrir una parte significativa de la demanda puntera nacional.

Preguntas frecuentes

¿Por qué no basta con traer fabs a EE. UU.?

Porque sin materiales (fotoresistentes, underfill), equipos y packaging localizados, la cadena sigue dependiendo de Asia y Europa. Las fabs no garantizan resiliencia por sí solas.

¿Qué significa exactamente “50/50”?

Hoy no está definido. Para ser operativo debe acotarse por familias (lógica puntera vs. nodos maduros), memoria, packaging y destinatarios (consumo USA total, gobierno, sectores críticos). Sin eso, es inmedible.

¿Quién pierde con un arancel del 100 %?

Probablemente, los fabricantes pequeños con menos capacidad de inversión en EE. UU. y clientes que compran chips de nodos maduros donde ya hay producción local suficiente. Las grandes (TSMC/Samsung) obtendrían exenciones por su inversión.

¿Cuándo podría EE. UU. cubrir “gran parte” de su demanda puntera?

Si TSMC Arizona, Intel y Samsung ejecutan calendarios, el salto relevante llegaría entre 2028 y principios de los 30. Para entonces, el foco deberá haberse extendido a materiales y packaging locales.

vía: tomshardware