La carrera por escalar la inteligencia artificial está empujando a la industria de los semiconductores hacia territorios que hace apenas unos años parecían ciencia ficción. El último movimiento llega desde Corea del Sur: según información publicada por medios especializados, Meta y NVIDIA están estudiando integrar núcleos de GPU directamente dentro de la memoria HBM de nueva generación, en colaboración con SK hynix y Samsung Electronics.

Si esta arquitectura llega a materializarse en productos comerciales, podría cambiar de raíz la forma en la que se diseñan los chips para centros de datos de IA y difuminar aún más la frontera entre memoria y procesador.

Qué es HBM y por qué todo gira a su alrededor

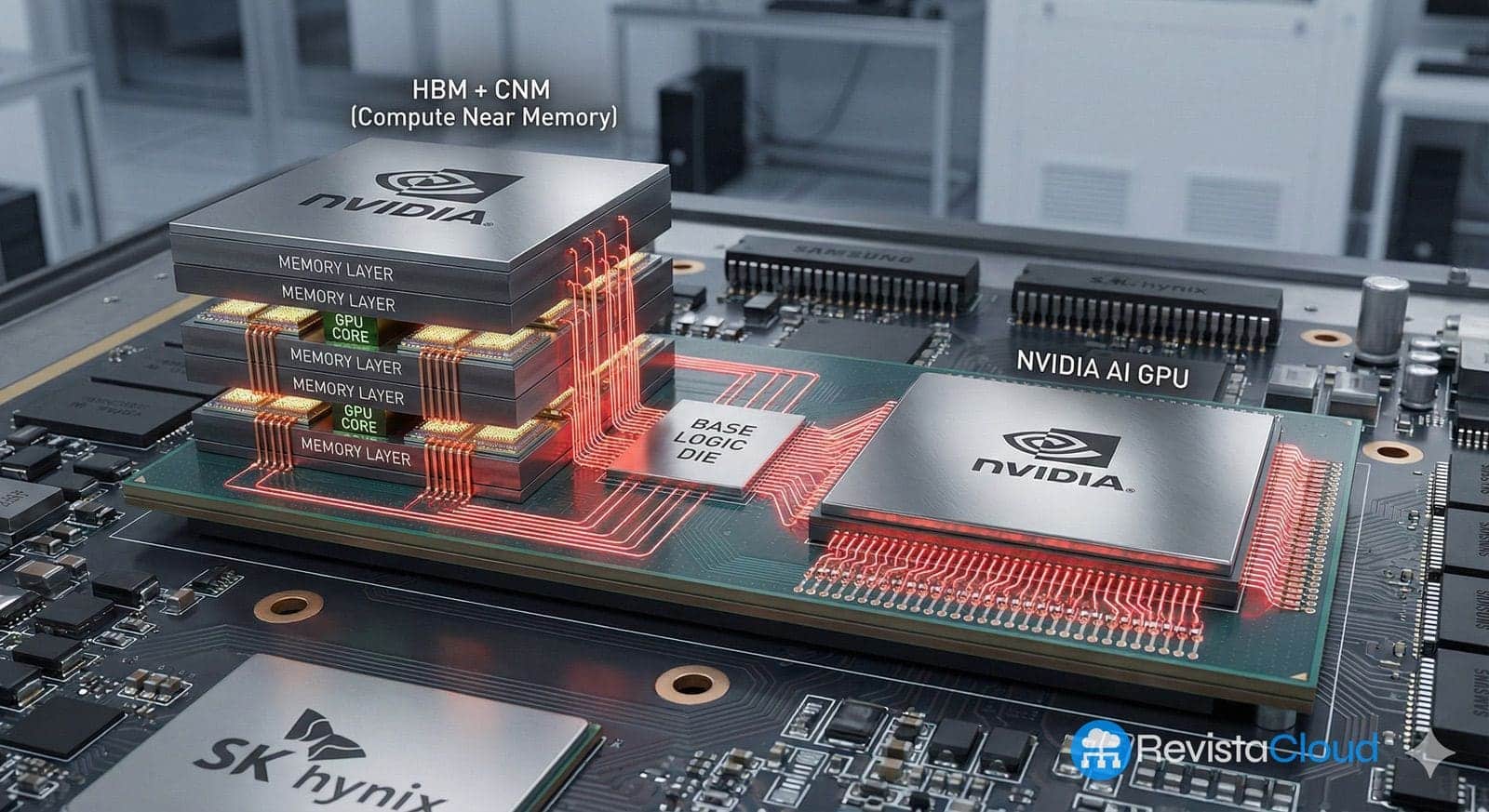

La HBM (High Bandwidth Memory) es un tipo de memoria creada para resolver un problema muy concreto: la falta de ancho de banda entre el procesador y la RAM en sistemas de alto rendimiento. En lugar de colocar los chips de memoria alrededor de la GPU o la CPU, HBM apila varias capas de DRAM una encima de otra y las conecta mediante TSV (Through-Silicon Vias), canales que atraviesan el silicio verticalmente.

Estas pilas de memoria se montan después sobre un interposer de silicio junto al procesador, en un empaquetado denominado habitualmente 2,5D. El resultado es un módulo compacto que ofrece:

- Muchísimo más ancho de banda que la memoria GDDR o DDR tradicional.

- Un consumo energético menor por bit transferido.

- Menor huella física alrededor del chip principal.

Por todo ello, HBM se ha convertido en la memoria de referencia para GPU de inteligencia artificial, aceleradores de cómputo y algunos procesadores de alto rendimiento. Los últimos desarrollos, como HBM3E y HBM4, llevan esta idea un paso más allá aumentando el número de capas, el bus de comunicación y las frecuencias para superar el umbral de los terabytes por segundo por pila de memoria.

Del “simple” controlador a los núcleos de GPU dentro del HBM

En la arquitectura actual, la HBM se limita, en esencia, a almacenar datos y servirlos lo más rápido posible al procesador externo. La pieza lógica situada en la parte inferior de la pila, el llamado base die, se encarga principalmente de gestionar las comunicaciones entre las capas de memoria y el resto del sistema.

Con HBM4 llega un primer cambio: algunos fabricantes empiezan a integrar controladores de memoria más avanzados y lógica adicional en ese base die. Esta lógica permite optimizar cómo se envían y reciben los datos, reducir latencias y mejorar la eficiencia sin modificar el chip principal.

La propuesta que ahora se discute va varios pasos más lejos. Según la información adelantada en Corea, Meta y NVIDIA están evaluando integrar núcleos de GPU en el propio base die de HBM, convirtiendo esa pieza en algo más que un simple gestor de memoria.

En la práctica, esto supondría que parte de la capacidad de cálculo que hoy reside exclusivamente en la GPU se desplazaría a la propia pila de memoria. Los núcleos de GPU integrados serían capaces de ejecutar operaciones sobre los datos sin necesidad de moverlos físicamente hasta el procesador principal.

Por qué acercar el cálculo a la memoria puede cambiar la IA

En los grandes centros de datos de inteligencia artificial, una buena parte del consumo energético y de los cuellos de botella no se deben tanto al cálculo en sí, sino al movimiento continuo de datos entre memoria y procesador. Cada salto implica latencia y gasto de energía.

La idea de integrar núcleos de GPU en la HBM apunta precisamente a ese problema:

- Menos distancia física entre donde se almacenan los datos y donde se procesan.

- Menos tráfico a través de los enlaces entre la HBM y la GPU principal.

- Posibilidad de ejecutar operaciones simples o repetitivas directamente en la memoria, dejando a la GPU central tareas más complejas.

Fuentes del sector citadas por la prensa surcoreana subrayan que, en IA, ya no se trata solo de “ir más rápido”, sino de mejorar la eficiencia energética por operación. Reducir unos nanosegundos de latencia y unos cuantos vatios por cada acelerador, multiplicado por decenas de miles de nodos en un centro de datos, puede traducirse en ahorros millonarios y en una menor presión sobre la red eléctrica.

El reto técnico: espacio, energía y calor en el base die

La teoría es atractiva, pero llevarla a la práctica no es trivial. El base die de HBM tiene varias limitaciones importantes:

- El proceso de fabricación con TSV deja poco espacio libre para lógica adicional. Hay que reservar buena parte de la superficie para las conexiones verticales que unen las distintas capas de memoria.

- Un núcleo de GPU, por pequeño que sea, consume energía y genera calor. Integrar varios de estos núcleos bajo una pila de DRAM apilada plantea desafíos de alimentación eléctrica y, sobre todo, de disipación térmica.

- El empaquetado 2,5D actual ya es complejo; añadir lógica de cálculo al base die obliga a replantear el diseño del interposer, las redes de distribución de energía y las soluciones de refrigeración.

Si los núcleos integrados consumen demasiado o se calientan en exceso, pueden afectar negativamente a la propia memoria, reduciendo su fiabilidad o su vida útil. El equilibrio entre capacidad de cálculo añadida y estabilidad del sistema será uno de los puntos críticos de esta posible arquitectura.

Meta, NVIDIA, SK hynix y Samsung: alianzas que rompen fronteras tradicionales

El hecho de que los nombres implicados sean Meta, NVIDIA, SK hynix y Samsung Electronics ilustra hasta qué punto el mapa del sector está cambiando. Tradicionalmente:

- Las empresas de memoria (SK hynix, Samsung, Micron) se enfocaban en DRAM y NAND.

- Las de lógica (NVIDIA, AMD, Intel, Qualcomm) diseñaban GPU, CPU y SoC.

La idea de integrar núcleos de GPU dentro del HBM obliga a trabajar codo con codo: se necesita experiencia puntera tanto en memoria como en lógica, además de capacidades avanzadas de foundry y empaquetado.

Para la industria surcoreana, esto es una mezcla de oportunidad y riesgo. Si compañías como SK hynix y Samsung logran ampliar su papel más allá de la memoria pura y se convierten en socios clave para este tipo de soluciones híbridas, podrán reclamar una posición central en la era de la IA.

Pero, si no consiguen dar el salto hacia el diseño de lógica y al ecosistema de “HBM personalizada”, podrían acabar subordinadas a los grandes diseñadores de sistemas, que usarían su capacidad de producción como una pieza más de un puzzle controlado desde fuera.

“La frontera entre memoria y lógica se está desvaneciendo”

Desde el mundo académico, expertos de instituciones como el KAIST (Instituto Avanzado de Ciencia y Tecnología de Corea) han subrayado que la tendencia es clara: la frontera entre memoria y sistema se está difuminando a gran velocidad a medida que la IA se vuelve más exigente.

El mensaje de fondo es que los fabricantes de memoria ya no pueden limitarse a mejorar densidad y velocidad; deben entrar también en el terreno de la lógica, ofrecer soluciones conjuntas y formar parte de un ecosistema que incluya desde el diseño del acelerador hasta el empaquetado avanzado y el software.

En este contexto, las discusiones sobre HBM con núcleos de GPU integrados no son una excentricidad aislada, sino un síntoma de un cambio de era: la memoria deja de ser un componente “pasivo” para convertirse en parte activa del cómputo.

HBM4, “custom HBM” y el camino hacia la computación bajo la memoria

La estandarización de HBM4 y los primeros anuncios comerciales de fabricantes como SK hynix y Samsung apuntan ya en esta dirección. La nueva generación de HBM incorpora:

- Interfaces de hasta 2.048 bits y velocidades previstas que superan los terabytes por segundo de ancho de banda por pila.

- Base dies más complejos, capaces de integrar controladores de memoria avanzados y lógica personalizada según el cliente.

- Técnicas de empaquetado como MR-MUF o NCF+TCB, que buscan mejorar la integridad térmica y mecánica de las pilas de memoria de 12 o 16 capas.

Sobre este terreno se construye la idea de la “custom HBM”, memorias HBM4 diseñadas a medida para un acelerador concreto, con el base die ajustado a las necesidades del chip principal. Integrar núcleos de GPU sería, en ese sentido, un paso adicional dentro de una tendencia que ya está en marcha: mover más inteligencia hacia la propia memoria.

Qué significaría para el futuro de los chips de IA

Si Meta y NVIDIA, junto con sus socios de memoria, consiguen superar las barreras técnicas y lanzar al mercado HBM con núcleos de GPU integrados, las consecuencias podrían ser profundas:

- Nueva categoría de aceleradores: GPU o XPU donde parte del cálculo se realiza directamente bajo la memoria, reduciendo el “muro de la memoria” que hoy limita muchos sistemas.

- Mayor fragmentación del mercado: cada gran proveedor de nube podría encargar su propia combinación de acelerador + HBM personalizada, dificultando la entrada de actores más pequeños.

- Presión adicional sobre la cadena de suministro: se necesitarán procesos lógicos avanzados para los base dies, capacidades de TSV y empaquetado de vanguardia, y una coordinación estrecha entre foundries y fabricantes de memoria.

A la vez, el movimiento consolidaría la importancia estratégica de la HBM como recurso crítico para la IA, reforzando la posición de los pocos países y empresas capaces de producirla a gran escala.

Por ahora, la integración de núcleos de GPU en HBM sigue en fase de estudio y discusión. Pero el solo hecho de que nombres como Meta, NVIDIA, SK hynix y Samsung la estén explorando indica que la carrera por romper el muro de la memoria ha entrado en una fase mucho más agresiva.

Preguntas frecuentes sobre HBM con núcleos de GPU integrados

¿Qué ventajas tendría integrar núcleos de GPU directamente en la memoria HBM para inteligencia artificial?

La principal ventaja sería reducir el movimiento de datos entre memoria y procesador. Al ejecutar parte de las operaciones directamente en el base die de la HBM, se disminuyen la latencia y el consumo energético asociados a esos traslados. Esto es especialmente relevante en centros de datos de IA, donde se manejan modelos gigantes y cargas de trabajo continuas, y cada mejora en eficiencia por vatio tiene un impacto económico y operativo muy elevado.

¿En qué se diferencia la HBM4 con controlador integrado de la propuesta de añadir núcleos de GPU?

La integración de un controlador de memoria en HBM4 busca optimizar cómo se gestionan las lecturas y escrituras, pero la función principal sigue siendo almacenar y servir datos rápidamente. Añadir núcleos de GPU supone ir más allá de la gestión y entrar en el terreno del cálculo activo, permitiendo realizar operaciones sobre los datos sin sacarlos de la pila de memoria. Son dos niveles distintos de integración: primero más inteligencia en la gestión, luego capacidad de cómputo real.

¿Qué desafíos técnicos existen para meter una GPU dentro de la memoria HBM?

Los principales retos son el espacio limitado en el base die debido a los TSV, el suministro de energía a núcleos que consumen bastante potencia y la gestión del calor bajo una pila de DRAM. Cualquier exceso de temperatura podría dañar la memoria o reducir su fiabilidad. Además, el empaquetado y la refrigeración del conjunto se vuelven más complejos, lo que exige nuevas soluciones de diseño y materiales.

¿Cómo puede afectar esta tendencia a la industria de semiconductores en Corea y a nivel global?

Para fabricantes como SK hynix y Samsung, la integración de lógica en HBM es una gran oportunidad para pasar de ser proveedores de memoria a actores centrales en los chips de IA. Pero también implica que quienes no consigan combinar memoria, lógica y empaquetado avanzado podrían quedar supeditados a los grandes diseñadores de aceleradores. A nivel global, esta convergencia refuerza el carácter estratégico de la cadena de suministro de HBM y aumenta la competencia por controlar tanto la producción de memoria como la de lógica avanzada.

Fuentes:

– Informaciones publicadas por ETNews sobre los planes de Meta y NVIDIA para integrar núcleos de GPU en el base die de HBM con SK hynix y Samsung.

– Documentación técnica y anuncios de la industria relativos a HBM3E y HBM4, JEDEC y fabricantes como SK hynix, Samsung y Micron.

– Análisis sectoriales sobre memoria de alto ancho de banda, empaquetado 2,5D y tendencias de “compute near memory” y “compute under memory” en aceleradores de IA.