La carrera por la Inteligencia Artificial no se está decidiendo solo en las GPU. El nuevo cuello de botella —silencioso, caro y cada vez más determinante— está en la memoria: en cuánta puede moverse por segundo, cuánta cabe cerca del procesador y cuánta energía se quema para mantener ese flujo constante de datos. En pleno 2026, con los centros de datos ampliándose a un ritmo que pone a prueba la red eléctrica y las cadenas de suministro, el foco se desplaza hacia un componente que durante años parecía “comoditizado”: la DRAM.

El síntoma es claro. Firmas como TrendForce han elevado con fuerza sus previsiones de subidas de precios para la memoria convencional, en un mercado tensionado por la demanda de infraestructura de IA y por la preferencia de los grandes fabricantes por destinar capacidad a productos más rentables como la HBM (High Bandwidth Memory). En paralelo, el impacto empieza a colarse en la electrónica de consumo: varios fabricantes de PCs han llegado a valorar, según información publicada en las últimas horas, alternativas de suministro en China ante la escasez global.

En ese contexto llega un movimiento llamativo: SoftBank, a través de su filial SAIMEMORY, y Intel han firmado un acuerdo de colaboración para avanzar en la comercialización de una tecnología denominada Z-Angle Memory (ZAM), una memoria de nueva generación pensada para combinar alta capacidad, alto ancho de banda y bajo consumo, con la mira puesta en cargas de trabajo de entrenamiento e inferencia de modelos a gran escala.

Un acuerdo con calendario: prototipos en el año fiscal 2027 y comercialización en 2029

La alianza se cerró el 2 de febrero de 2026 y el plan oficial marca hitos concretos: prototipos durante el año fiscal que termina el 31 de marzo de 2028 (FY2027) y objetivo de comercialización en FY2029. SAIMEMORY, creada en diciembre de 2024, liderará el desarrollo y la salida al mercado, mientras que Intel aportará base tecnológica y soporte de innovación.

SoftBank encuadra esta apuesta dentro de su estrategia para reforzar infraestructura vinculada a centros de datos e IA, insistiendo en un cambio de fase: del entrenamiento masivo a la inferencia operativa, donde mover grandes volúmenes de datos hacia los aceleradores se vuelve crítico.

¿Qué es ZAM y por qué importa el “eje Z”?

ZAM se presenta como una arquitectura de memoria que mira hacia arriba: el propio nombre alude al eje Z, es decir, a apilar estructura en vertical para aumentar capacidad y rendimiento sin disparar el tamaño físico. El objetivo, en términos sencillos, es acercar más memoria “rápida” a los chips que hacen la computación, reduciendo fricciones típicas: latencia, consumo y limitaciones de empaquetado.

Aunque el proyecto aún está en una etapa temprana, varios análisis sectoriales lo sitúan como un intento de superar las limitaciones actuales de la HBM, que ha sido clave para la IA por su enorme ancho de banda, pero que también impone compromisos en capacidad y costes. De hecho, el razonamiento de fondo es que el sector necesita memorias que no obliguen a elegir siempre entre “más ancho de banda” o “más capacidad”.

La pieza técnica que trae Intel: Next Generation DRAM Bonding (NGDB)

El corazón tecnológico del acuerdo está en el trabajo previo de Intel bajo su iniciativa Next Generation DRAM Bonding (NGDB), desarrollada dentro del programa Advanced Memory Technology (AMT) gestionado por el Departamento de Energía de EE. UU. y la National Nuclear Security Administration, con apoyo de laboratorios nacionales como Sandia.

Sandia ha explicado públicamente avances relevantes: su descripción apunta a que, en la memoria de alto ancho de banda, a menudo se mejora el ancho de banda a costa de degradar otros factores, como capacidad. NGDB buscaría reducir ese intercambio, “acercando” prestaciones entre HBM y la DRAM convencional con mejoras de eficiencia energética. En una de sus actualizaciones, el laboratorio muestra ensamblajes de prueba con una capa base y ocho capas DRAM apiladas verticalmente, y subraya que los prototipos más recientes ya demostraban DRAM funcional mediante ese método de apilado.

La propia Sandia resume la ambición con una frase que, sin necesidad de hype, deja claro por qué este tema importa: hacer memoria de alto rendimiento “apta para fabricación a gran escala”.

Dinero, industria y la batalla por el suministro

Aunque el comunicado oficial pone el foco en la hoja de ruta, medios especializados han señalado que SoftBank planea invertir del orden de 3.000 millones de yenes para llegar al hito de prototipos del año fiscal 2027, cifra atribuida a fuentes sectoriales citadas en cobertura especializada.

El movimiento también se entiende como una apuesta estratégica: Japón fue un actor relevante en memoria en décadas anteriores y hoy busca posiciones en áreas críticas de la cadena de valor de la IA. ZAM, si madura, no solo sería un componente: sería una palanca para reducir dependencia tecnológica en un mercado donde la demanda se ha vuelto política, industrial y geopolítica al mismo tiempo.

Y es que el contexto global no da tregua: la escasez de memoria y la reasignación de capacidad hacia productos para IA está alterando precios, planificación de lanzamientos y decisiones de abastecimiento, desde los centros de datos hasta el portátil de consumo.

Lo que queda por demostrar

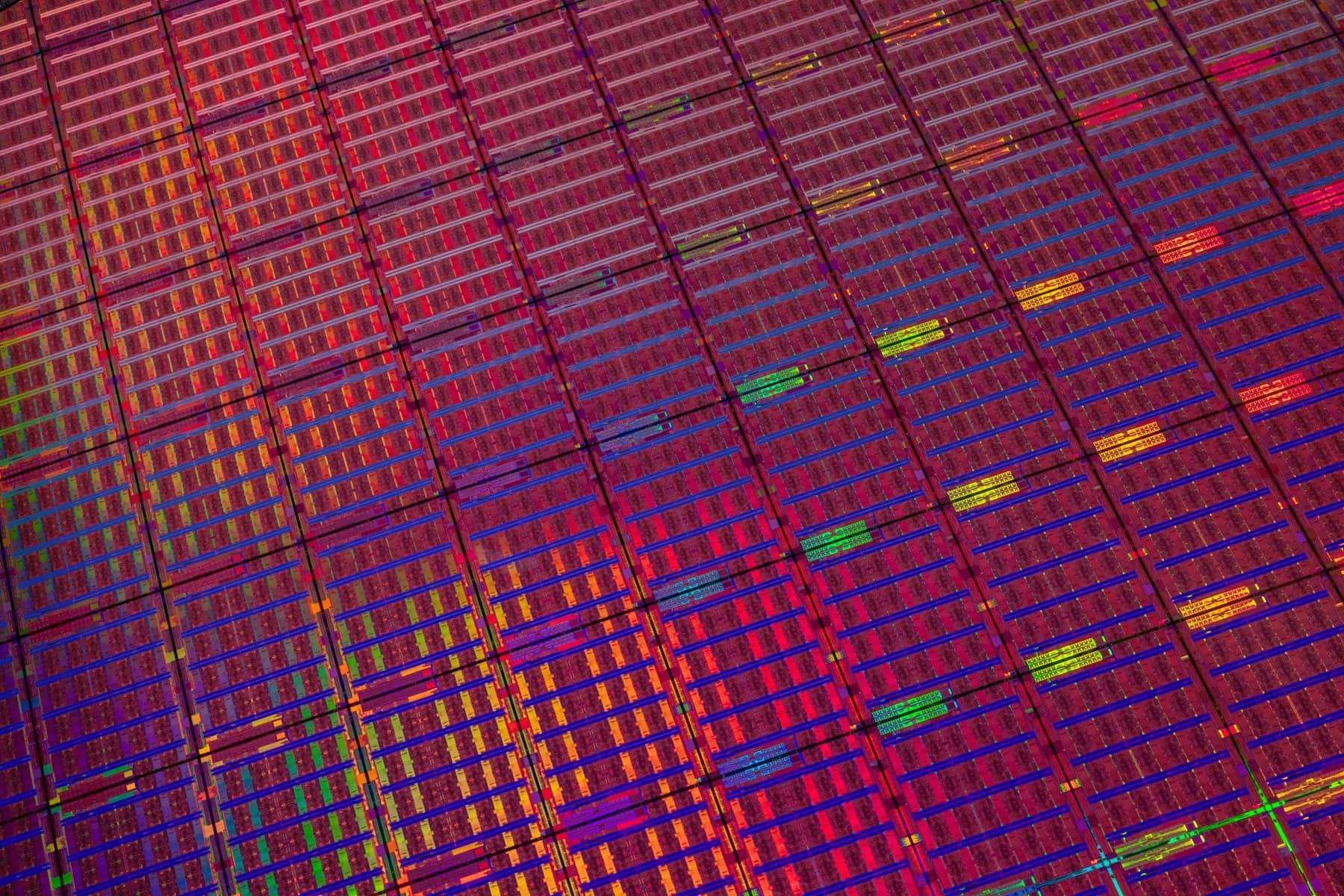

A día de hoy, ZAM es una promesa con calendario, no un producto en estantería. Entre el anuncio y la fabricación a gran escala hay un camino de obstáculos conocidos en semiconductores: rendimiento por oblea (yield), disipación térmica en apilados densos, complejidad de empaquetado, estandarización para integrarse en plataformas de servidores y, sobre todo, coste real frente a alternativas consolidadas.

Pero el mensaje de mercado es difícil de ignorar: si la IA es una carrera de infraestructuras, la memoria se está convirtiendo en el tramo donde más fácil es tropezar. Y cuando el sector se tropieza, nacen oportunidades para arquitecturas nuevas, alianzas improbables y reentradas históricas.

Preguntas frecuentes

¿Qué diferencia a la memoria HBM de la DRAM “normal” (DDR4/DDR5) en servidores de IA?

HBM prioriza un ancho de banda altísimo gracias a su empaquetado avanzado y cercanía al chip de cómputo, algo crucial para alimentar GPUs/accelerators; DDR se usa como memoria principal general, normalmente con más flexibilidad y menor coste por capacidad, pero con menos ancho de banda por paquete.

¿Cuándo podrían verse los primeros sistemas comerciales con Z-Angle Memory (ZAM)?

El plan comunicado apunta a prototipos en el año fiscal 2027 y a comercialización en el año fiscal 2029, por lo que su llegada a productos finales dependerá de la industrialización y de acuerdos con fabricantes de plataformas.

¿Por qué la memoria se ha convertido en un cuello de botella para la Inteligencia Artificial?

Los modelos grandes y la inferencia a escala necesitan mover datos de forma continua hacia aceleradores. Si falta ancho de banda o capacidad cercana al cómputo, la GPU puede quedarse “esperando”, y eso encarece cada entrenamiento y cada servicio.

¿Cómo afecta la escasez de DRAM y NAND a usuarios de PC y empresas?

Cuando suben los precios o hay restricciones de suministro, los fabricantes ajustan configuraciones, retrasan lanzamientos o buscan proveedores alternativos; en empresas, el impacto puede traducirse en mayores costes de servidores, ampliaciones y renovaciones.

vía: trendforce