Intel y SoftBank, a través de SAIMEMORY, han dejado ver nuevos detalles de HB3DM, una memoria 3D basada en Z-Angle Memory (ZAM) que aspira a convertirse en una alternativa a la HBM tradicional para cargas de inteligencia artificial y computación de alto rendimiento. No es una memoria comercial lista para sustituir mañana a HBM4 en aceleradores de NVIDIA, AMD o Intel, pero sí una propuesta técnica interesante en un momento en el que el ancho de banda de memoria se ha convertido en uno de los grandes límites de la infraestructura de IA.

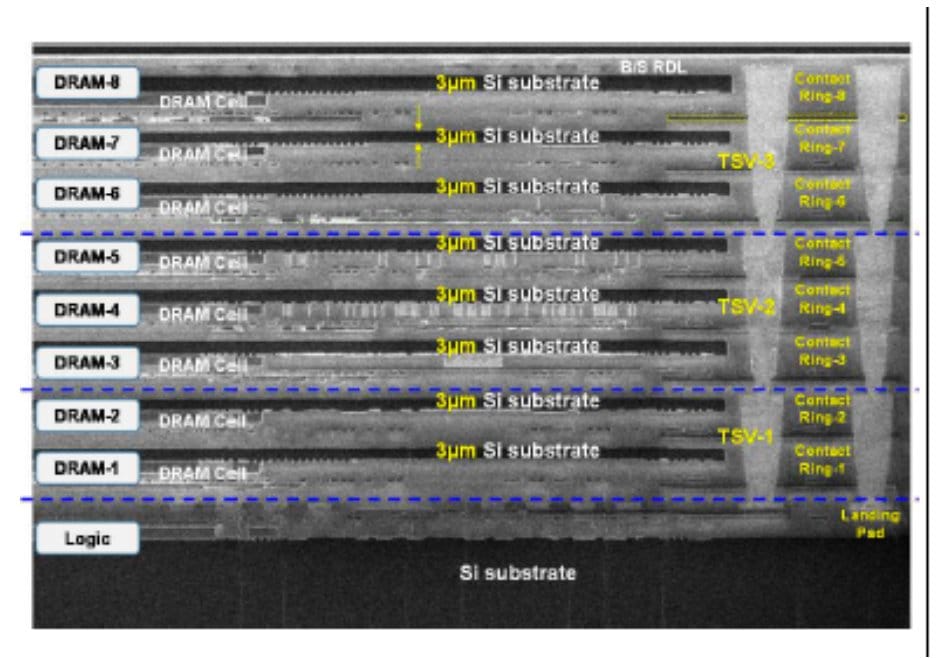

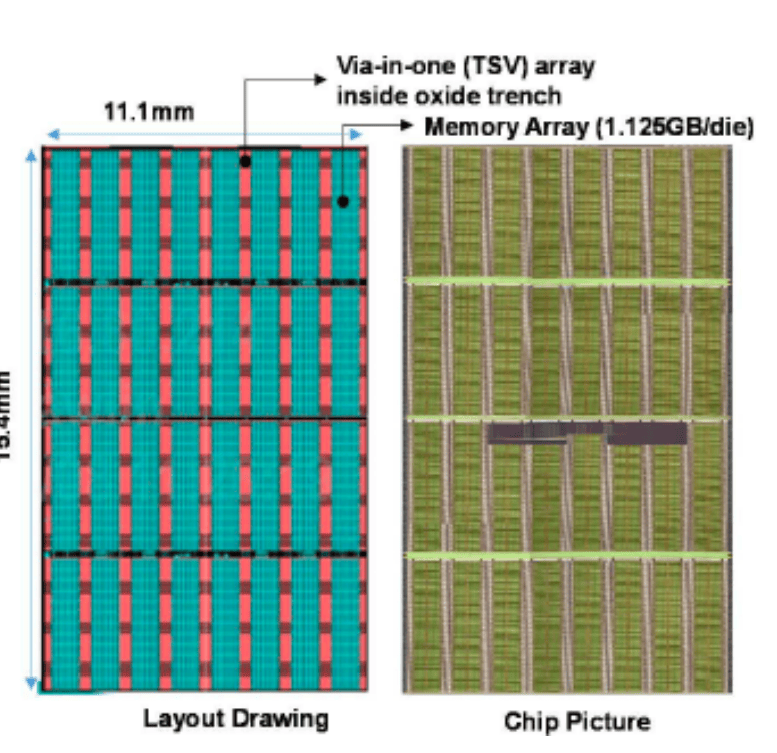

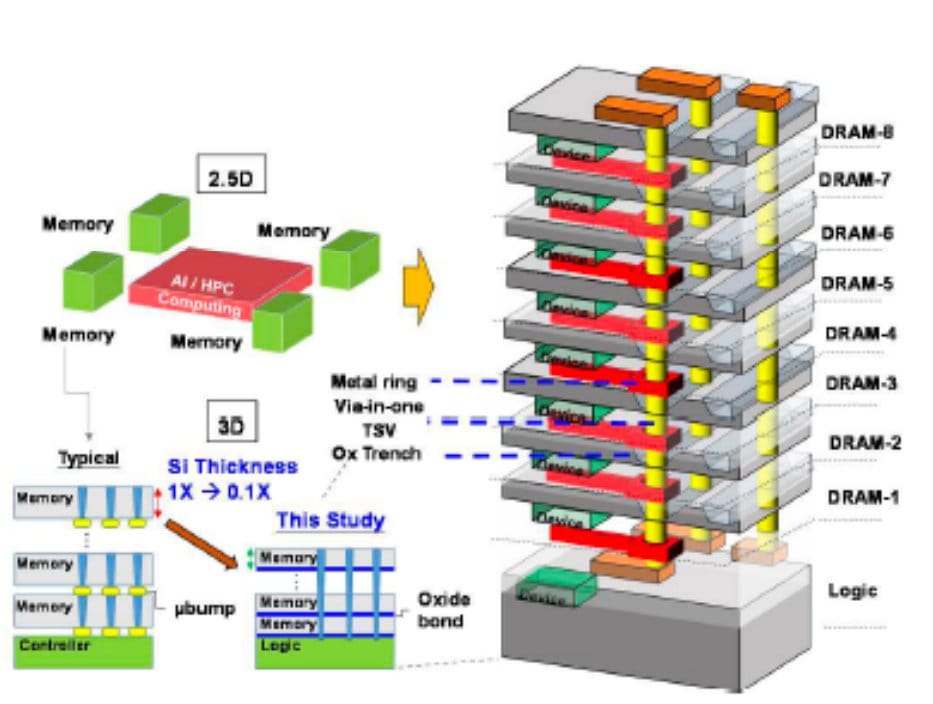

La información procede de los datos asociados a una ponencia prevista para el VLSI Symposium 2026, que se celebrará en junio en Honolulu. Según los detalles difundidos, la primera demostración de HB3DM utiliza un apilado de nueve capas: una capa lógica en la base y ocho capas DRAM encima, conectadas mediante hybrid bonding y con un sustrato de silicio muy fino, de solo 3 µm por capa DRAM.

Qué propone HB3DM frente a HBM

La memoria HBM actual ya se basa en apilar chips DRAM y conectarlos verticalmente mediante TSV, pero HB3DM intenta llevar esa integración a un diseño todavía más denso. La capa lógica inferior se encarga de gestionar el movimiento de datos, mientras que las capas de DRAM almacenan la información. La promesa es clara: más ancho de banda por superficie, menor consumo y una arquitectura más adaptada a aceleradores de inteligencia artificial.

SoftBank anunció en febrero que su filial SAIMEMORY había firmado un acuerdo con Intel para avanzar en la comercialización de Z-Angle Memory, una tecnología de memoria de nueva generación diseñada para alta capacidad, alto ancho de banda y bajo consumo. La compañía fijó como objetivo crear prototipos en el ejercicio fiscal 2027 y alcanzar la comercialización en el ejercicio fiscal 2029.

La parte técnica conocida de HB3DM deja varias cifras llamativas. Cada capa integraría alrededor de 13.700 TSV, el die tendría un área de 171 mm² y el ancho de banda se situaría en 0,25 Tb/s por mm². Aplicado a esa superficie, el resultado ronda los 5,3 TB/s por stack. En capacidad, la propuesta se mueve en torno a los 9-10 GB por módulo, bastante por debajo de los 36 GB o 48 GB que ya se manejan en HBM4.

| Característica | HB3DM/ZAM, según datos difundidos |

|---|---|

| Estructura | 1 capa lógica + 8 capas DRAM |

| Total de capas | 9 |

| Grosor de sustrato DRAM | 3 µm por capa |

| Conexión vertical | Hybrid bonding |

| TSV por capa | Unos 13.700 |

| Capacidad estimada | En torno a 9-10 GB por stack |

| Área del die | 171 mm² |

| Densidad de ancho de banda | 0,25 Tb/s/mm² |

| Ancho de banda estimado | Aproximadamente 5,3 TB/s por stack |

| Objetivo de prototipo | Ejercicio fiscal 2027 |

| Objetivo comercial | Ejercicio fiscal 2029 |

La comparación con HBM4 requiere matices. Micron, por ejemplo, habla de HBM4 con interfaz de 2.048 pines, velocidades superiores a 11 Gbps y más de 2,8 TB/s por stack en su generación actual, además de muestras de HBM4 de 48 GB en configuración 16-high. HB3DM apunta a más ancho de banda por stack en los datos publicados, pero ofrece bastante menos capacidad. Para cargas de inteligencia artificial, ambas variables importan: no basta con mover datos muy rápido si no caben suficientes datos cerca del procesador.

Una arquitectura prometedora, pero aún temprana

Intel y SAIMEMORY no están presentando una memoria lista para producción masiva. La hoja de ruta oficial habla de prototipos primero y comercialización más adelante. Esto sitúa HB3DM en una fase de validación técnica, no en una alternativa inmediata para los aceleradores que llegarán al mercado en 2026 y 2027.

Ese calendario importa porque HBM tampoco está parada. SK hynix, Samsung y Micron trabajan ya en HBM4 y HBM4E, con más capacidad, mayor ancho de banda y base dies cada vez más sofisticados. Para cuando ZAM llegue a fase comercial, el mercado podría estar mirando a HBM5 o a variantes específicas para clientes de gran escala.

Aun así, el concepto tiene sentido. La demanda de memoria de alto ancho de banda se ha disparado por la inteligencia artificial. Los modelos de lenguaje, los sistemas multimodales, los agentes y las cargas de inferencia necesitan mover grandes volúmenes de datos con baja latencia y consumo contenido. La escasez y el coste de HBM han creado espacio para enfoques alternativos, aunque ninguno lo tendrá fácil.

El papel de Intel es especialmente interesante. La compañía salió hace años del negocio de memoria convencional, pero conserva conocimiento en empaquetado avanzado, interconexión y tecnologías de apilado. SoftBank explica que SAIMEMORY aprovechará tecnologías y experiencia validadas por la iniciativa Next Generation DRAM Bonding de Intel, desarrollada dentro de programas estadounidenses de memoria avanzada.

Eso no significa necesariamente que Intel vaya a fabricar DRAM de forma convencional en sus propias fábricas. De momento, no está claro quién producirá las capas de memoria subyacentes ni cómo se organizará la cadena industrial. TrendForce señala precisamente que aún no se conoce cuándo SAIMEMORY planea comercializar estos chips ni qué proveedor fabricará la DRAM base, aunque la implicación de Intel alimenta la idea de un posible regreso indirecto al terreno de la memoria avanzada.

Más ancho de banda, menos capacidad

El gran atractivo de HB3DM está en el ancho de banda. Un stack capaz de rondar los 5,3 TB/s sería muy competitivo para determinadas cargas donde el procesador necesita acceder a datos de forma continua. La densidad por superficie también puede ayudar a diseñar aceleradores más compactos o con más canales de memoria en el mismo espacio de empaquetado.

La limitación está en la capacidad. Un módulo de unos 10 GB queda lejos de las cifras actuales y futuras de HBM4. Para entrenamiento de modelos grandes, capacidad y ancho de banda deben crecer juntas. Si un acelerador necesita muchos stacks de HB3DM para igualar la capacidad de una configuración HBM4, el beneficio de ancho de banda podría verse compensado por mayor complejidad de empaquetado, coste o consumo total.

Por eso HB3DM no debe verse únicamente como “el sustituto de HBM”. Puede terminar encajando en nichos concretos: aceleradores de inferencia, diseños donde prime el ancho de banda extremo, sistemas HPC especializados o incluso productos propios de Intel si la compañía decide diferenciarse de la ruta seguida por NVIDIA y AMD.

También habrá que comprobar la eficiencia térmica. Los stacks de memoria muy densos tienen un problema físico evidente: disipar calor entre capas. La propuesta ZAM habla de menor consumo y de una estructura pensada para mejorar la disipación, pero hasta que existan prototipos medidos en condiciones reales será difícil saber cuánto de esa ventaja llega a un sistema completo.

La cifra de hasta un 40 % menos de consumo frente a HBM tradicional, recogida en informaciones sobre ZAM, sería muy relevante si se confirma en producto. En centros de datos de inteligencia artificial, cada vatio cuenta: no solo por la factura eléctrica, sino por refrigeración, densidad por rack, estabilidad y capacidad de despliegue.

Una señal de que la memoria será el nuevo campo de batalla

HB3DM llega en un momento en el que la industria está redescubriendo algo que los arquitectos de sistemas llevan años repitiendo: el cálculo no sirve de mucho si la memoria no alimenta al procesador al ritmo adecuado. La inteligencia artificial ha convertido esa limitación en un problema comercial de primer orden.

Hasta ahora, la conversación pública se ha centrado en GPUs, aceleradores y nodos de fabricación. Pero el cuello de botella de la memoria está ganando protagonismo. HBM es cara, difícil de fabricar, limitada en suministro y muy exigente en empaquetado. Si una alternativa logra ofrecer más ancho de banda, menos consumo o mejor escalabilidad, tendrá mercado.

La cuestión es si ZAM puede pasar de demostración técnica a producto fabricable, rentable y compatible con las necesidades de los grandes diseñadores de aceleradores. La historia del hardware está llena de arquitecturas prometedoras que no superaron el salto industrial. En memoria, ese salto es especialmente duro: requiere rendimiento, fiabilidad, capacidad, coste, producción en volumen y años de validación con clientes.

Intel y SoftBank han puesto sobre la mesa una idea que merece atención, pero todavía necesita pruebas. HB3DM no desbanca a HBM4 por una tabla de ancho de banda. Tendrá que demostrar que puede escalar, que su capacidad mejora, que su fabricación es viable y que los integradores de aceleradores la ven como algo más que una curiosidad técnica.

Lo interesante es que la carrera ya no se limita a hacer más rápida la HBM existente. La presión de la IA está abriendo caminos alternativos en memoria 3D, empaquetado, chiplets, interconexión y consumo. HB3DM es una de esas rutas. Si funciona, Intel podría volver a tener una voz relevante en memoria avanzada. Si no, al menos confirma hacia dónde se mueve el sector: la próxima batalla de la IA también se librará en los micrómetros que separan una capa de memoria de otra.

Preguntas frecuentes

¿Qué es HB3DM?

HB3DM es una propuesta de memoria 3D basada en Z-Angle Memory, desarrollada en el marco de la colaboración entre Intel y SAIMEMORY, filial de SoftBank. Busca ofrecer alto ancho de banda y bajo consumo para inteligencia artificial y HPC.

¿En qué se diferencia de HBM?

HB3DM también utiliza apilado vertical, pero apuesta por una integración 3D muy fina, con capas DRAM de 3 µm, hybrid bonding y una capa lógica inferior para gestionar el movimiento de datos.

¿Es ya una alternativa comercial a HBM4?

No. La tecnología está en fase de demostración técnica. SoftBank habla de prototipos en el ejercicio fiscal 2027 y comercialización en el ejercicio fiscal 2029.

¿Cuál es su principal ventaja y su principal límite?

La ventaja más clara es el ancho de banda estimado, de unos 5,3 TB/s por stack. El límite principal es la capacidad inicial, alrededor de 9-10 GB por stack, por debajo de las cifras actuales de HBM4.

News from @Intel and @SoftBank SAIMEMORY from @VLSI_2026

— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) April 29, 2026

Paper T17.5

First demo of HB3DM

➡️ 9 layer, 3 micron per stack

➡️ 1 logic + 8 DRAM layers,

➡️ 13.7k TSVs/layer with hybrid bonding

➡️ 1.125 GB/layer, so 10 GB per stack

➡️ 0.25 Tb/sec/mm2 bandwidth

➡️ 171 mm2 die, so 10… pic.twitter.com/q79qV4sRdT