Intel ha vuelto a poner el foco en un terreno donde se juega buena parte del futuro de los procesadores para IA y centros de datos: cómo seguir aumentando la capacidad de cómputo cuando un único “die” ya no puede crecer indefinidamente por límites físicos y de coste. La idea no es nueva —la industria lleva años abrazando el diseño por chiplets—, pero el mensaje que Intel está intentando consolidar es ambicioso: el tamaño deja de ser un problema de litografía y pasa a ser, sobre todo, un problema de integración avanzada.

En otras palabras: si el límite de la retícula (reticle limit) impide fabricar un chip monolítico más grande, la salida es construir “sistemas” dentro de un único paquete, sumando módulos de cómputo y memoria y uniéndolos con interconexiones de muy alta velocidad, como si fueran piezas de un LEGO para arquitectos de silicio. Este enfoque no promete un producto concreto con cifras cerradas, pero sí marca una dirección clara para competir en el segmento más caro y estratégico del mercado.

Por qué la retícula ya manda menos que antes

En litografía, la retícula define el área máxima que puede exponerse en una sola pasada. Cuando un diseño supera ese tamaño, el monolito se vuelve inviable o prohibitivamente caro. El cambio de paradigma consiste en dividir el chip en “tiles” y recomponerlo en el empaquetado: el paquete se convierte en el verdadero “sustrato de innovación”.

En la práctica, este enfoque permite mezclar nodos (fabricar distintos bloques en procesos diferentes), escalar el cómputo por modularidad y colocar memoria de alto ancho de banda (HBM) cerca del silicio, algo clave en aceleradores de IA.

La pieza base: 18A-PT y la energía “por detrás”

Uno de los conceptos más interesantes que Intel está empujando es el de un Compute Base Die: una base sobre la que apilar y conectar el resto de tiles. En el marco de Intel Foundry, la compañía ha descrito una variante de su nodo 18A, llamada 18A-PT, pensada para integrar tecnologías avanzadas de empaquetado y servir de “suelo” del sistema.

Aquí entra en juego un factor técnico con implicación económica: la entrega trasera de energía (backside power delivery). Separar rutas de potencia y señal ayuda a ganar densidad y mejorar el comportamiento eléctrico, algo crítico cuando se apilan bloques y se suben consumos. Intel enmarca estas técnicas dentro de su hoja de ruta de procesos y de su oferta foundry para atraer clientes que quieren alternativas a TSMC en nodos punteros.

EMIB-T: más ancho de banda para unir “tiles” y memoria

El otro gran pilar es la interconexión. Intel ha ido evolucionando EMIB (Embedded Multi-die Interconnect Bridge) como un “puente” dentro del paquete para conectar chiplets sin necesidad de un gran interposer. La variante EMIB-T añade TSVs (vías a través del silicio) para aumentar ancho de banda y habilitar integraciones más grandes y complejas. En la narrativa de Intel, esto está pensado, entre otras cosas, para acompañar el salto de la memoria HBM hacia futuras generaciones y necesidades de ancho de banda cada vez más extremas.

Dicho de forma simple: si el chip se vuelve un “campus”, EMIB-T es una autopista más ancha, con más carriles y menos cuellos de botella, para que cómputo y memoria puedan hablar a la velocidad que exige la IA moderna.

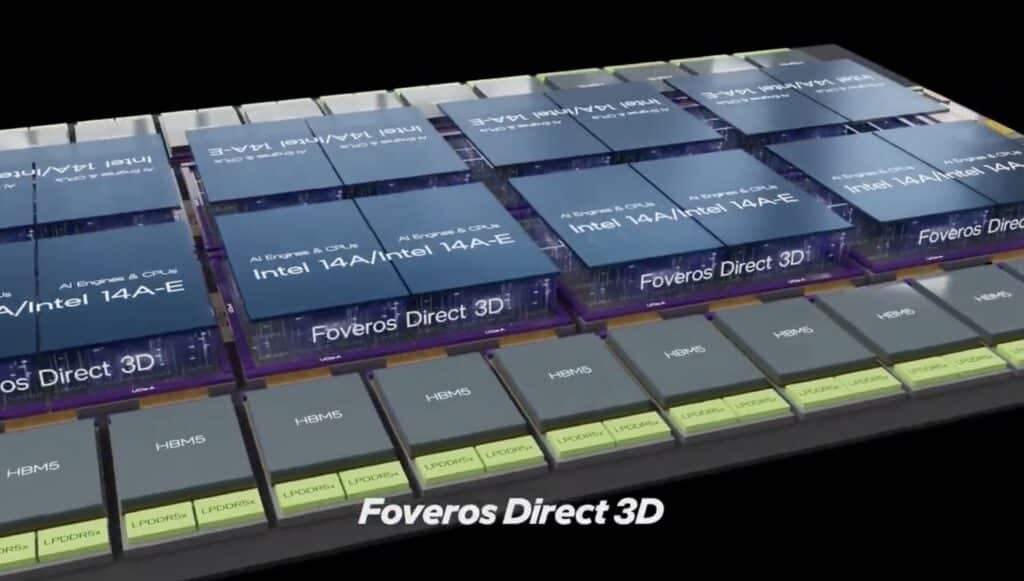

Foveros Direct: el 3D deja de ser marketing y se vuelve método

En paralelo, Intel insiste en Foveros Direct, su enfoque de unión 3D mediante hybrid bonding (unido directo con paso muy fino). La promesa aquí es reducir distancias, mejorar eficiencia y permitir apilado real para sistemas multichip, conectando capas con latencias menores que en enfoques más “2,5D”. Intel lo presenta como parte de la receta para escalar paquetes más complejos y con más densidad de interconexión.

El contexto de negocio: la IA está rompiendo el mercado… también en empaquetado

Este discurso no aparece en el vacío. La demanda de aceleradores de IA ha convertido el empaquetado avanzado en un recurso crítico: no basta con fabricar buen silicio; hay que encapsularlo con memoria y enlaces de alta velocidad. Reuters y otros seguimientos del sector llevan tiempo señalando el cuello de botella de capacidad en empaquetado avanzado (y la carrera por ampliarla) como uno de los factores que condicionan plazos y márgenes en la era de la IA.

Ahí Intel ve una oportunidad: si consigue posicionar su combinación de proceso + empaquetado + ecosistema como oferta completa de foundry, puede jugar en una mesa donde el precio por wafer no lo es todo. La diferenciación pasa por “el sistema completo”: integración, suministro, capacidad industrial y tiempos.

Lo que falta: fechas, métricas y, sobre todo, adopción real

Hay una razón por la que estas presentaciones suelen venir cargadas de diagramas y ligeras de números: convertir integración avanzada en producción masiva es difícil. En el mundo real, la viabilidad depende de rendimientos (yield), defectos, validación térmica, test, costes de ensamblado y, crucialmente, de que haya clientes dispuestos a apostar por la plataforma.

Intel sí ha puesto encima de la mesa su hoja de ruta (con 18A y el futuro 14A como siguientes pasos), y ha asociado esas generaciones a avances como PowerVia/PowerDirect y técnicas de empaquetado. Pero el mercado no premiará promesas: premiará volúmenes, estabilidad y la capacidad de entregar “a tiempo y a escala”.

Qué debería vigilar el mercado en 2026–2027

Para el sector —y para cualquiera que siga la batalla Intel vs TSMC/Samsung— el “futuro multichip” se medirá en señales concretas:

- acuerdos foundry que incluyan empaquetado avanzado como parte del contrato;

- demostraciones de integración con HBM y enlaces chiplet de alta velocidad en diseños reales;

- madurez de herramientas, IP y estándares (UCIe y derivados) que reduzcan fricción a los clientes;

- capacidad industrial: empaquetado, test y cadena de suministro, no solo litografía.

Si Intel logra convertir este enfoque en una propuesta repetible para terceros, el multichip dejará de ser un “mensaje de arquitectura” y pasará a ser una ventaja competitiva cuantificable.

Preguntas frecuentes

¿Qué significa “límite de la retícula” y por qué importa?

Es el tamaño máximo del patrón que puede exponerse en litografía de una sola vez. Limita el tamaño de chips monolíticos y empuja a usar chiplets y empaquetado avanzado para escalar.

¿EMIB y Foveros son lo mismo que un interposer tipo CoWoS?

No exactamente. CoWoS suele basarse en un interposer grande; EMIB usa “puentes” embebidos para conectar chiplets. Foveros apunta a apilado 3D (conexión vertical). Son enfoques distintos para el mismo objetivo: más ancho de banda y más integración.

¿Por qué la HBM es tan importante en IA?

Porque aporta muchísimo ancho de banda y reduce latencia al estar muy cerca del chip de cómputo. En IA, mover datos es tan crítico como computar.

¿Esto llegará a PC y consumo o es solo para centros de datos?

El camino suele ser: primero centros de datos (por márgenes y necesidad), y más tarde versiones recortadas en consumo cuando bajan costes y madura el empaquetado. El ritmo dependerá del coste y la disponibilidad industrial.

From cutting-edge interconnects to system-level assembly and test, Intel Foundry delivers the scale and integration needed to power next-generation multichip platforms. https://t.co/smSje92QQh #IntelFoundry #Semiconductors pic.twitter.com/4sAVftVRhg

— Intel Foundry (@Intel_Foundry) December 22, 2025