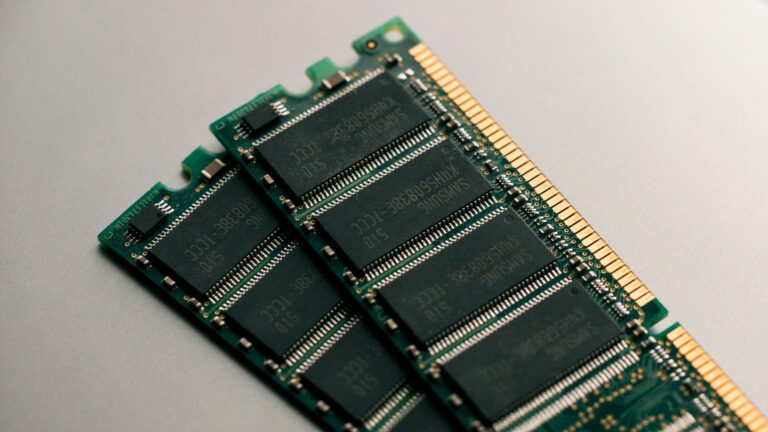

Intel sopesa otra subida de precios en CPU mientras la IA aprieta la oferta

Intel podría volver a subir el precio de sus procesadores en mayo, según nuevos informes de canal publicados en Asia y replicados por medios especializados. Por ahora no existe un anuncio público de Intel que confirme una nueva ronda concreta para mayo, así que ese movimiento debe tratarse como un rumor con base en comprobaciones de canal, no como una decisión oficial cerrada. Lo que sí está confirmado es el contexto: Intel lleva meses reconociendo que no puede cubrir toda la demanda de CPU para centros de datos de IA y que su capacidad sigue tensionada. La cuestión, por tanto, ya no es solo si habrá otra subida, sino por qué el mercado la considera verosímil. Reuters informó en enero