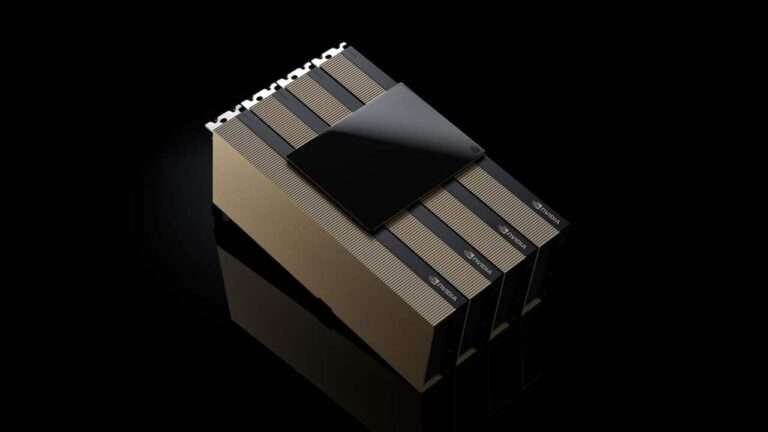

Facturas, servidores y sanciones: China reabre el caso Nvidia

La presión sobre el control de las GPU avanzadas hacia China ha vuelto a subir de nivel tras la aparición de documentos fiscales y financieros que apuntan a la compra de casi 300 servidores de IA por parte de una empresa china vinculada al ecosistema de centros de datos. El caso no prueba por sí solo una violación de las restricciones de exportación de Estados Unidos, pero sí vuelve a poner en cuestión hasta qué punto ese cerco tecnológico está funcionando en la práctica. La empresa en el centro de la historia es Sharetronic Data Technology, con sede en Shenzhen. Según informó Bloomberg tras revisar registros de facturación de la Administración Tributaria china, la compañía vendió a una filial en