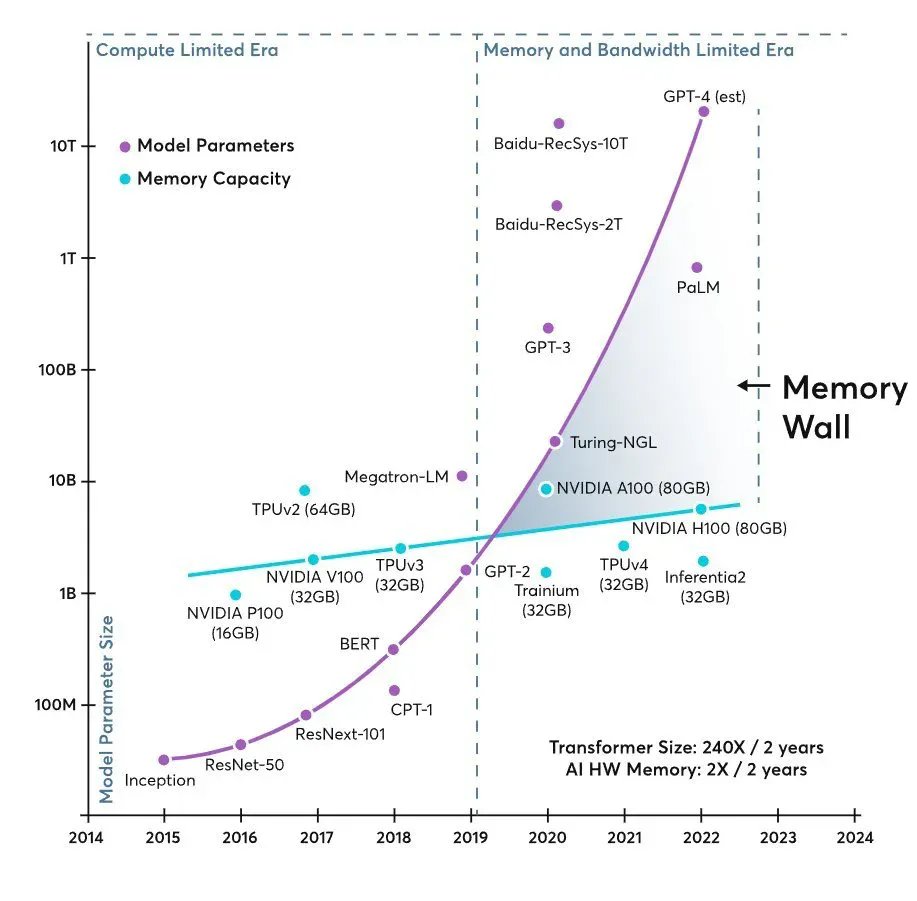

Durante años, la conversación sobre infraestructura para Inteligencia Artificial se ha explicado con una idea simple: “faltan GPUs”. Pero en 2026, el cuello de botella empieza a contarse de otra forma. Una gráfica muy difundida en círculos técnicos e inversores muestra dos curvas que se separan como tijeras: el tamaño de los modelos crece de manera casi exponencial, mientras que la memoria disponible por acelerador avanza a un ritmo mucho más modesto. El resultado es el mismo en cualquier centro de datos: si el procesador gráfico no recibe datos a la velocidad adecuada, su potencia queda infrautilizada, aunque el hardware sea de última generación.

Esta tensión se resume en un término que cada vez aparece con más frecuencia en documentos académicos y en blogs especializados: “memory wall” o pared de memoria. No se trata únicamente de “falta de memoria”, sino del conjunto de capacidad, ancho de banda y latencia necesarios para mover datos entre la lógica de cómputo y los distintos niveles de memoria (desde cachés on-chip hasta HBM o DRAM). En modelos tipo transformer —especialmente en el servicio de inferencia—, la memoria y su ancho de banda pueden convertirse en el factor dominante frente al cómputo puro, con impacto directo en coste, consumo y latencia.

De la era del cómputo a la era de alimentar al acelerador

La industria ya había vivido algo parecido en la computación tradicional: CPUs cada vez más rápidas esperando a que la RAM les sirviera datos. En IA, la película se repite, pero a escala industrial. A medida que los modelos crecen, también crecen los requisitos de mover parámetros, activaciones, embeddings y, en inferencia, cachés internas que permiten mantener contexto. Cuando ese “tren de datos” no llega a tiempo, el acelerador pasa parte de su ciclo esperando.

En ese contexto, la inversión empieza a desplazarse: no basta con instalar más GPUs; también hay que diseñar sistemas capaces de mantenerlas ocupadas, con memoria más cercana, más ancha y con más capacidad utilizable. Por eso, las discusiones técnicas se han llenado de siglas que antes eran casi invisibles para el gran público: HBM, CXL, jerarquías de memoria más complejas, y arquitecturas que intentan reducir el coste de “mover bytes” frente a “hacer operaciones”.

HBM y DDR5: la memoria vuelve al centro del diseño

La High Bandwidth Memory (HBM) se ha convertido en el símbolo de esta nueva etapa porque ataca el problema por donde más duele: ancho de banda por vatio y cercanía física al chip. Los propios fabricantes de memoria ya posicionan sus gamas más avanzadas como la “alimentación” necesaria para entrenamiento de modelos exigentes, mientras reservan DDR5 para escalabilidad y coste en configuraciones más generalistas. En su material técnico, Micron Technology destaca HBM3E y DDR5 para cargas de entrenamiento y, a la vez, propone módulos de expansión basados en CXL como vía para ampliar capacidad más allá de los canales directos cuando el problema es el “tamaño total” del dataset o del modelo.

Esta estrategia ilustra una idea cada vez más aceptada: el futuro inmediato no es elegir “una memoria”, sino mezclar capas (HBM para velocidad, DDR para volumen y extensiones tipo CXL para crecer sin rehacer toda la plataforma). En el mundo real, esto se traduce en racks con más complejidad y, también, más dependencia de la cadena de suministro de memoria avanzada.

El otro gran invitado: flash para checkpoints y almacenamiento rápido

El debate no se queda en HBM. Los flujos de entrenamiento y servicio de modelos grandes dependen de checkpoints, datasets masivos y almacenamiento local rápido para evitar que el clúster se convierta en una máquina de “esperar a disco”. De ahí que el mercado esté observando un aumento de tracción para NAND y SSD empresariales: no solo por capacidad, sino por rendimiento sostenido y latencias predecibles.

En ese tablero, el protagonismo de SanDisk ha vuelto con fuerza tras su separación corporativa, completada el 24 de febrero de 2025, cuando pasó a operar como compañía independiente y a cotizar con el ticker SNDK. En sus resultados recientes, distintos medios financieros han vinculado el salto de ingresos y beneficios a la demanda impulsada por IA y a la presión sobre la oferta, hasta el punto de hablar de contratos plurianuales y precios más firmes para asegurar suministro.

Para un medio tecnológico, la lectura es pragmática: cuanto más crecen los modelos, más se profesionaliza el “backstage” del entrenamiento y la inferencia. La IA no vive solo en el chip; vive en la tubería completa, desde la memoria de muy alta velocidad hasta el almacenamiento que sostiene datasets, checkpoints y artefactos de despliegue.

Micron, inversión y capacidad: la memoria como apuesta industrial

La presión no se nota solo en el catálogo de productos, sino también en inversiones a gran escala. En enero de 2026, Reuters informó de que Micron planea invertir 24.000 millones de dólares en una nueva planta de fabricación en Singapur para atender la escasez global de memoria ligada al auge de aplicaciones de IA y cargas “data-centric”. La misma información señalaba que Singapur ya concentra el grueso de su producción de flash y que la compañía cuenta allí con una planta de empaquetado avanzado para HBM valorada en 7.000 millones de dólares, con contribución prevista a partir de 2027.

Al margen del detalle geográfico, el mensaje es claro: la memoria se está convirtiendo en un componente estratégico, no accesorio. Y cuando la industria entra en esa dinámica, el impacto se extiende a todo: disponibilidad, precios, tiempos de entrega y decisiones de arquitectura dentro de los centros de datos.

Hiperescalares y el coste de mantener la GPU “con hambre cero”

Los grandes operadores cloud —Google, Amazon, Meta y Microsoft— compiten por entrenar y servir modelos cada vez más exigentes. La narrativa habitual se centra en compras masivas de aceleradores de NVIDIA, pero en la práctica el reto es sostener una “fábrica” donde los chips estén ocupados la mayor parte del tiempo.

En esta conversación, la gráfica de la “pared de memoria” funciona como metáfora útil: por un lado, la industria celebra modelos cada vez mayores (incluidas estimaciones no oficiales atribuidas a OpenAI), y por otro, el hardware necesita más memoria y más ancho de banda para que ese tamaño sea utilizable con eficiencia. Si el sistema no alimenta bien, la solución no siempre es “comprar más GPU”, sino aumentar memoria por acelerador, mejorar la red interna y optimizar el flujo de datos.

La próxima ola: arquitectura, no solo potencia bruta

El giro más interesante de esta etapa es que la innovación se está desplazando hacia la arquitectura del sistema: cómo se distribuyen parámetros, cómo se gestiona la caché en inferencia, cómo se reduce el tráfico de memoria o cómo se mueve menos información para obtener el mismo resultado. La pared de memoria no se derriba con una sola pieza, sino con un conjunto: HBM más capaz, mejores interconexiones, almacenamiento local rápido, y diseños que aceptan que “mover datos” es el nuevo lujo.

En el corto plazo, la consecuencia más visible será una: los centros de datos de IA tenderán a ser más caros y más complejos, pero también más optimizados. Y en ese camino, la memoria —HBM y flash— deja de ser un complemento para convertirse en el eje que decide si un clúster rinde al 30 % o se acerca a su potencial real.

Preguntas frecuentes

¿Qué significa exactamente “memory wall” en modelos de lenguaje y por qué afecta tanto a la inferencia?

La “pared de memoria” describe el punto en el que el rendimiento queda limitado por capacidad, latencia o ancho de banda de memoria, no por el cómputo. En inferencia, la necesidad de mantener y mover datos de contexto y estructuras internas puede convertir la memoria en el cuello de botella principal.

¿HBM3E es imprescindible o DDR5 sigue siendo válida para cargas de IA?

HBM3E suele usarse cuando el objetivo es máximo ancho de banda y eficiencia energética para entrenamiento de alto nivel. DDR5 sigue siendo muy útil por coste y escalabilidad, especialmente en configuraciones donde la capacidad total pesa más que el pico de rendimiento.

¿Qué papel juega la memoria flash (SSD/NVMe) en centros de datos de IA?

La flash es clave para almacenamiento rápido de datasets, checkpoints y operaciones que requieren I/O sostenido. Un subsistema de almacenamiento lento puede frenar pipelines de entrenamiento y procesos de despliegue incluso con GPUs potentes.

¿Cómo encaja CXL en la estrategia para superar la falta de memoria en servidores de IA?

CXL permite ampliar capacidad de memoria de forma más flexible que los canales tradicionales, aportando una vía para escalar volumen cuando el límite ya no es solo el ancho de banda, sino la capacidad total necesaria para datos y modelos.

vía: X Twitter