En la carrera por exprimir cada vatio y cada hercio, la industria del chip se está encontrando con un enemigo incómodo: la alimentación eléctrica ya no escala tan bien como los transistores. Cuanto más denso y más rápido es un procesador, más difícil resulta mantener estable la tensión que llega a los bloques de cómputo cuando millones (o miles de millones) de transistores cambian de estado al mismo tiempo. Ese instante de caída de tensión —el temido voltage droop— es uno de esos problemas poco “glamurosos” que, sin embargo, puede decidir si un chip aguanta frecuencias altas, si reduce rendimiento para protegerse o si consume más de lo deseable.

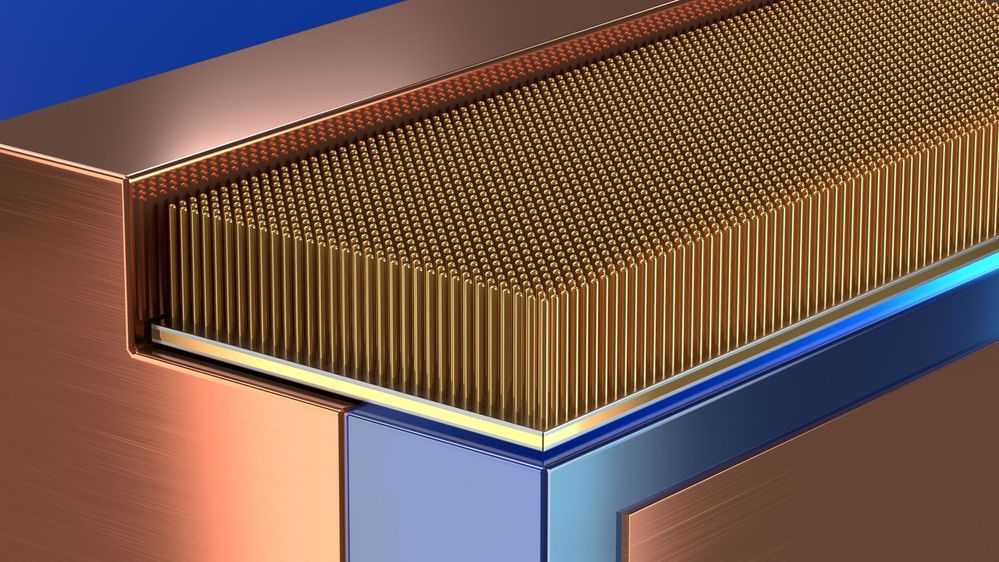

Ahí entra la última línea de investigación que Intel e Intel Foundry han presentado como avance clave: nuevos materiales para condensadores integrados metal-insulator-metal (MIM) destinados a mejorar la entrega de energía dentro del propio chip. Traducido: más “capacidad eléctrica” en menos superficie, sin convertir la fabricación en un infierno de capas extra y procesos carísimos.

¿Qué se ha anunciado exactamente?

Los investigadores han mostrado tres opciones de materiales MIM con densidades de capacitancia intrínseca que alcanzan hasta 98 fF/µm², muy por encima del valor de referencia citado para materiales de última generación (37 fF/µm²). La cifra importa porque los condensadores de desacoplo (DCAP) actúan como pequeños “depósitos” de carga: cuando la CPU o el acelerador pega un pico de demanda, ese depósito suministra corriente de inmediato y ayuda a mantener la tensión estable.

Intel detalla tres rutas:

- Hafnio-zirconio óxido ferroelectrico (HZO): aprovecha una respuesta dieléctrica dependiente del campo eléctrico para ofrecer 60–80 fF/µm².

- Óxido de titanio (TiO): llega a ~80 fF/µm² gracias a una constante dieléctrica muy alta.

- Óxido de titanato de estroncio (STO): alcanza 98 fF/µm², el mayor valor mostrado en la demostración.

Más allá del dato “de récord”, Intel insiste en el paquete completo: fugas por debajo de objetivos, estabilidad durante pruebas prolongadas y proyecciones de fiabilidad a largo plazo a 90 °C, un punto crítico porque los DCAP deben resistir calor sostenido dentro de chips muy exigentes.

Por qué este avance es relevante (aunque no suene a revolución)

En un centro de datos, especialmente en cargas de Inteligencia Artificial, el rendimiento por vatio es la nueva moneda. No se trata solo de que un chip sea rápido; se trata de cuánto tiempo puede sostener ese rendimiento sin entrar en límites térmicos o de potencia. Una alimentación más estable ayuda a mantener frecuencias altas durante más tiempo y a evitar “dientes de sierra” de rendimiento. En móvil, una entrega de energía más eficiente no solo afecta a picos de rendimiento: también facilita transiciones más rápidas a estados de bajo consumo, lo que se traduce en mejor autonomía en uso real.

Además, el mensaje industrial de Intel es claro: muchas mejoras históricas de capacitancia han venido por “trucos” de integración (más capas, zanjas más profundas, más complejidad). Los materiales, en cambio, prometen un salto sin disparar la complejidad de fabricación, y con compatibilidad con estructuras MIM avanzadas integradas (Intel menciona arquitecturas MIM integradas dentro de su enfoque de fabricación).

La tabla rápida: qué aporta cada material

| Material (MIM) | Densidad de capacitancia citada | Rasgo clave | Nota de fiabilidad destacada |

|---|---|---|---|

| HZO (ferroelectrico) | 60–80 fF/µm² | Respuesta dieléctrica dependiente del voltaje (capacitancia “reactiva”) | Estabilidad prolongada y proyección de vida útil a alta temperatura |

| TiO (alta-k) | ~80 fF/µm² | Constante dieléctrica muy elevada con baja dependencia de voltaje | Buen margen a tensiones altas; análisis de fugas con mecanismo Poole–Frenkel |

| STO (ultra alta-k) | 98 fF/µm² | Máxima densidad demostrada | Cumple objetivos en escenarios de menor voltaje; aún con margen de optimización de proceso |

Lo que hay detrás: la batalla contra el “droop” y el coste de fabricarlo

Intel explica el problema con una lógica sencilla: cuando el chip demanda corriente de golpe, si la energía no llega lo bastante rápido, cae la tensión y el sistema se protege bajando frecuencias o perdiendo estabilidad. Los DCAP son el “amortiguador” que permite absorber esas sacudidas. Pero fabricar DCAP mejores suele implicar más superficie o más complejidad.

La vía de los materiales intenta evitar el peaje: en vez de apilar y complicar, aumentar la “capacidad por área” del propio dieléctrico. Si esa mejora se integra en estructuras MIM ya contempladas en procesos avanzados, el impacto puede ser transversal: CPUs, GPUs, NPUs, aceleradores… todo lo que sufra picos de consumo.

¿Cuándo se notará en productos?

Intel sitúa el trabajo como una demostración de investigación presentada en el circuito técnico (IEDM 2025) y lo vende como un camino “multigeneracional”: materiales que podrían aportar mejoras en varias generaciones de proceso sin necesidad de reinventar el flujo de fabricación. Eso no implica que mañana vayamos a ver “el chip con HZO” en un producto concreto, pero sí dibuja una prioridad real: la alimentación interna del chip es ya un límite de rendimiento tan serio como el nodo litográfico o la arquitectura de núcleos.

Preguntas frecuentes

¿Qué es un condensador de desacoplo (DCAP) y por qué importa en una CPU o GPU?

Es un condensador integrado que actúa como reserva instantánea de corriente para estabilizar la tensión cuando el chip pega picos de consumo; ayuda a reducir caídas de voltaje que pueden forzar bajadas de frecuencia o inestabilidad.

¿Por qué se mide en fF/µm² y qué significa que sea “más alto”?

Es la capacitancia (femtofaradios) que se obtiene por cada micrómetro cuadrado de área. Cuanto más alta, más “capacidad eléctrica” cabe en el mismo espacio del chip.

¿Esto mejora el rendimiento en juegos o solo en centros de datos?

Puede ayudar en ambos: una entrega de energía más estable favorece picos sostenidos de rendimiento. Donde más se nota es en cargas intensivas (IA, HPC, creación) y en escenarios donde el chip alterna rápidamente entre estados de consumo.

¿Por qué Intel habla de materiales (HZO, TiO, STO) y no de “más capas”?

Porque añadir capas o estructuras más complejas suele encarecer y complicar la fabricación. La vía de materiales busca subir la capacitancia sin disparar la complejidad del proceso.

vía: community.intel