El negocio del equipamiento semiconductor de back-end empieza a ocupar un lugar mucho más visible en la industria global del chip. Un informe comercial de The Business Research Company sitúa este mercado por encima de los 34.000 millones de dólares en 2030, con Asia-Pacífico como región dominante y China como principal país por volumen previsto. Son cifras que conviene leer con cautela, porque proceden de estudios de mercado privados y no de estadísticas oficiales auditadas, pero reflejan una tendencia que sí encaja con el momento del sector: el ensamblado, el empaquetado y el test final se han convertido en una pieza crítica para sacar adelante chips cada vez más complejos.

La razón de fondo no está solo en fabricar más, sino en fabricar mejor. La ola de demanda ligada a la Inteligencia Artificial, la memoria HBM, la computación de alto rendimiento y los diseños basados en chiplets ha empujado a toda la cadena de valor a prestar mucha más atención a la fase final del proceso. SEMI prevé que el segmento de back-end mantenga el crecimiento en 2026, con el test subiendo un 12,0 % y el ensamblado y empaquetado un 9,2 %, impulsados por la mayor complejidad de las arquitecturas y por las exigencias de rendimiento de los chips para Inteligencia Artificial y HBM.

Del encapsulado clásico al empaquetado avanzado

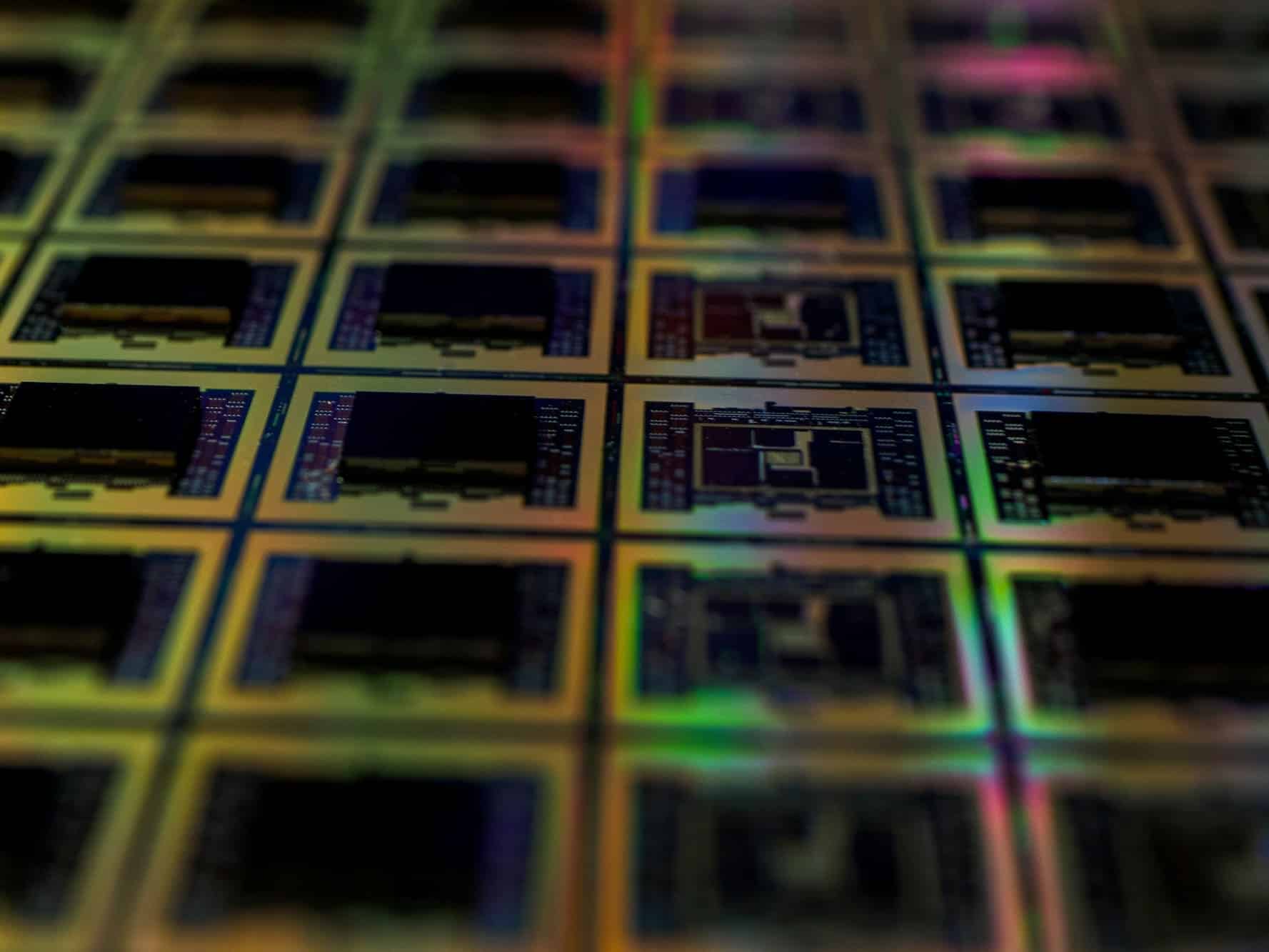

Cuando se habla de back-end se hace referencia, en términos generales, a la parte final de la fabricación semiconductor: preparación del dado, die bonding, wire bonding, encapsulado, ensamblado y test. No es una fase menor ni meramente logística. Ahí se juega buena parte de la fiabilidad del componente, su disipación térmica, su consumo, su integración con memoria o sustratos avanzados y, en última instancia, su rendimiento real una vez sale al mercado. Las descripciones comerciales del propio mercado sitúan entre los grandes bloques de este negocio el die bonding, el wire bonding, el packaging y los sistemas de test.

Ese cambio de peso industrial se ve con claridad en la estrategia de los grandes fabricantes. TSMC lleva años insistiendo en que el valor ya no reside solo en el nodo de fabricación, sino también en la capacidad de integrar varios chips como un sistema. Su plataforma 3DFabric agrupa tecnologías como SoIC, CoWoS e InFO, y la compañía la presenta como una combinación de tecnologías front-end y back-end orientadas a resolver problemas de integración heterogénea y acelerar la llegada a volumen. En otras palabras, el empaquetado ha dejado de ser la última casilla del proceso para convertirse en un factor de competitividad.

La tracción ya se nota en los resultados de varias compañías especializadas. ASMPT informó de unos ingresos de 532,1 millones de dólares en su negocio de advanced packaging en 2025, un 30,2 % más interanual, con un fuerte empuje de sus soluciones TCB. Besi, uno de los nombres más observados en este nicho, elevó en 2025 sus objetivos financieros a largo plazo al apuntar a una mayor demanda de soluciones de advanced packaging para lógica y memoria. Y Teradyne cerró el cuarto trimestre de 2025 con 883 millones de dólares en Semiconductor Test dentro de unos ingresos totales de 1.083 millones, apoyados por la demanda relacionada con Inteligencia Artificial en computación, redes y memoria. No son movimientos aislados: reflejan que el cuello de botella del chip ya no está solo en la oblea, sino también en cómo se empaqueta y se valida.

Asia concentra el gasto y China sigue marcando el ritmo

El informe comercial difundido esta semana señala que Asia-Pacífico podría alcanzar los 17.000 millones de dólares en 2030 dentro de este mercado, mientras China rondaría por sí sola los 10.000 millones. La tesis encaja con la geografía real del sector: es en Asia donde se concentra gran parte de la capacidad de ensamblado, test y packaging, y donde operan muchos de los grandes OSAT y fabricantes con mayor músculo industrial. También es donde más se nota la combinación de ayudas públicas, presión por la autosuficiencia tecnológica y expansión de capacidad.

Los datos de SEMI van en la misma dirección, aunque no midan exactamente el mismo subsegmento. La asociación prevé que China, Taiwán y Corea del Sur sigan siendo los principales destinos del gasto en equipamiento semiconductor hasta 2027. En Taiwán, buena parte del tirón sigue vinculado a capacidad de vanguardia para Inteligencia Artificial y computación de alto rendimiento. En China, el peso continúa siendo enorme incluso con una moderación prevista tras varios años de inversiones muy agresivas. Esa combinación ayuda a explicar por qué el back-end gana tanto protagonismo: no solo importa abrir fábricas, también importa disponer de la maquinaria capaz de ensamblar, encapsular y testear chips cada vez más exigentes.

Un mercado al alza, pero con previsiones que conviene matizar

La historia, con todo, no debería leerse como si existiera una única cifra incuestionable. Otro estudio comercial, publicado por ResearchAndMarkets, dibuja un escenario algo más prudente: 23.540 millones de dólares en 2026 y 32.760 millones en 2030. La diferencia respecto al umbral de los 34.000 millones no cambia la tendencia de fondo, pero sí recuerda que estos informes trabajan con metodologías, definiciones y perímetros distintos. En mercados tan especializados, una variación en lo que cada firma considera “back-end equipment” puede mover miles de millones sobre el papel.

Lo importante, más allá de la cifra exacta, es el mensaje industrial. La fase final del chip ya no puede tratarse como una actividad secundaria ni como un eslabón de bajo valor añadido. La expansión de la Inteligencia Artificial, la memoria avanzada, los chiplets y el empaquetado 2.5D y 3D está desplazando inversión hacia las máquinas que unen, encapsulan, conectan y prueban esos componentes. El mercado del back-end seguirá siendo más pequeño que el del equipamiento front-end, pero cada vez será más estratégico para decidir qué empresas pueden escalar producción, mejorar rendimiento y capturar valor en la nueva carrera del semiconductor.

Preguntas frecuentes

¿Qué significa back-end en la fabricación de chips?

Se refiere a la parte final del proceso de fabricación semiconductor, donde el chip se corta, se une al sustrato o al encapsulado, se conecta, se protege y se somete a pruebas antes de su salida comercial. Incluye equipos de die bonding, wire bonding, packaging y test.

¿Por qué el empaquetado avanzado es tan importante en 2026?

Porque los chips para Inteligencia Artificial, HBM y computación de alto rendimiento necesitan integrar varios dados, memoria y sustratos avanzados con mayor densidad, mejor gestión térmica y más ancho de banda. TSMC, por ejemplo, presenta sus tecnologías CoWoS, InFO y SoIC como parte central de esa evolución.

¿Qué empresas se benefician más del auge del back-end semiconductor?

Entre las más expuestas están fabricantes de equipos de ensamblado, packaging y test como ASMPT, Besi y Teradyne. Sus resultados recientes muestran que la demanda de soluciones ligadas al empaquetado avanzado y al test de chips para Inteligencia Artificial está creciendo con fuerza.

¿Asia seguirá liderando este mercado en los próximos años?

Todo apunta a que sí. Los informes comerciales sitúan a Asia-Pacífico como la región dominante, y SEMI prevé que China, Taiwán y Corea del Sur sigan encabezando el gasto en equipamiento semiconductor durante los próximos años.

vía: semiconductors news