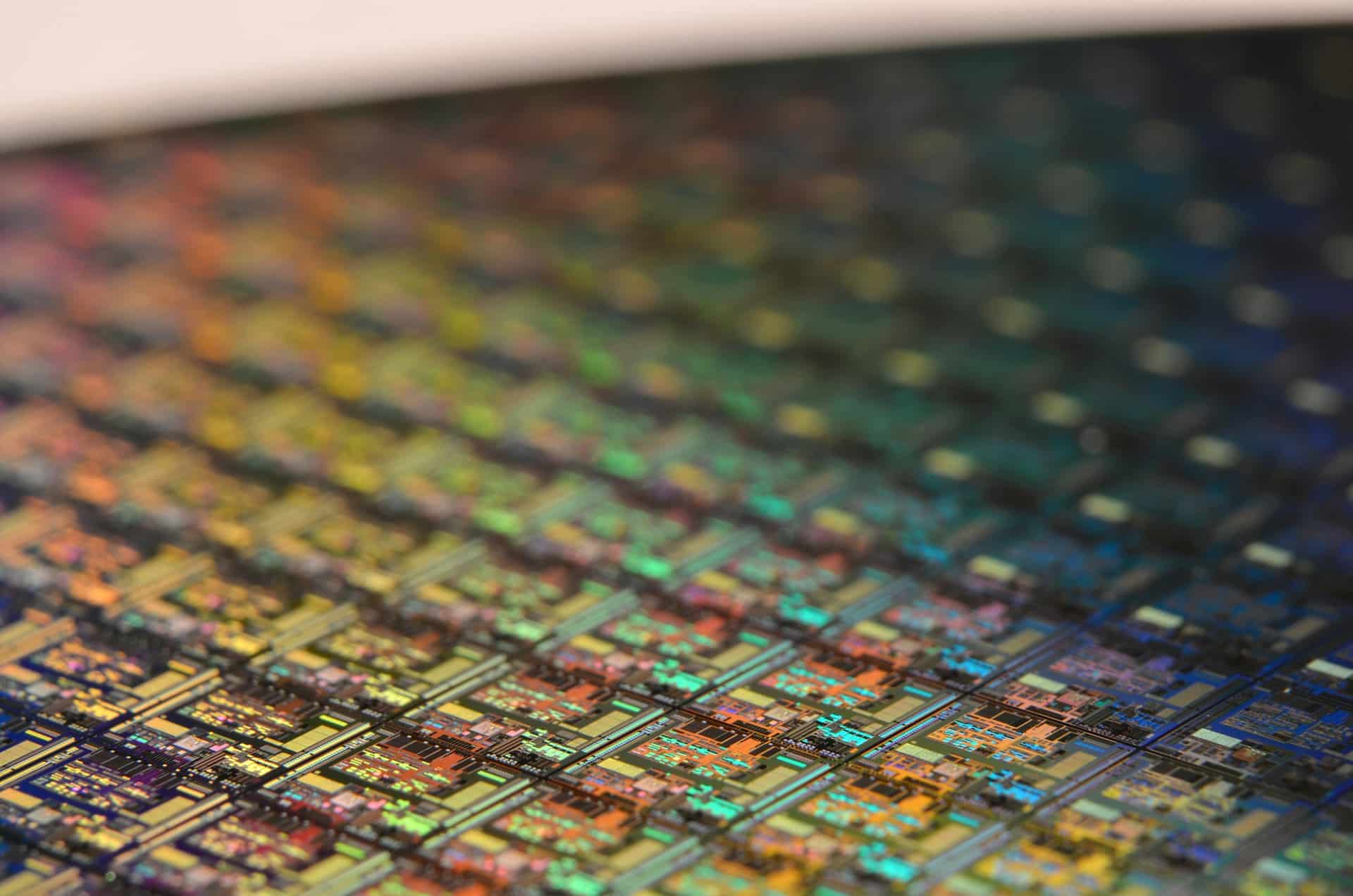

El sector de los semiconductores lleva años acostumbrado a los grandes titulares sobre miniaturización, pero el salto que plantea ahora la industria surcoreana apunta a una frontera que, hasta hace poco, sonaba más a laboratorio que a hoja de ruta. El Instituto Coreano de Ingenieros de Semiconductores (The Institute of Semiconductor Engineers) ha publicado su “Semiconductor Technology Roadmap 2026”, un documento que proyecta la evolución tecnológica de los próximos 15 años y que sitúa el horizonte de 2040 como el inicio de una nueva etapa: la llegada de circuitos lógicos “de 0,2 nm” y el desembarco de estructuras como CFET y el 3D monolítico.

La previsión, difundida por ETNews, habla de una reducción drástica del tamaño de los circuitos —hasta una décima parte respecto a los niveles actuales— y del paso desde la escala del “nanómetro” hacia la escala del “ångström” (A), una unidad que se utiliza cuando se opera ya en rangos de décimas de nanómetro.

De los 2 nm actuales al gran salto de 2040

La hoja de ruta llega en un momento en el que la industria empieza a consolidar la transición a arquitecturas de transistores más avanzadas. Samsung, por ejemplo, ha presentado su Exynos 2600 como un chip móvil basado en un proceso GAA (Gate-All-Around) de 2 nm, un hito que marca el listón de lo “puntero” en 2025. A partir de ahí, el roadmap coreano plantea un camino de mejoras continuas que debería desembocar, hacia 2040, en nodos lógicos “de 0,2 nm”, apoyados en dos conceptos clave:

- CFET (Complementary Field-Effect Transistor): una evolución del transistor que busca apilar y combinar dispositivos complementarios para seguir escalando densidad y rendimiento.

- Estructuración 3D monolítica: una aproximación que pretende ir más allá del apilado tradicional (packaging avanzado) y construir capas funcionales integradas de forma mucho más estrecha.

En la práctica, el mensaje de fondo es claro: si el escalado “plano” se acerca a sus límites, la industria necesita más verticalidad y nuevas arquitecturas para seguir avanzando.

La letra pequeña del “0,2 nm”: más que una cifra, un símbolo

La cifra “0,2 nm” es potente, pero también delicada. En el mundo real, los nombres de nodo no siempre equivalen a una medida física única (como la longitud de puerta), y suelen condensar múltiples mejoras: densidad, eficiencia, rendimiento, nuevos materiales y reglas de diseño. Por eso, cuando un roadmap habla de “0,2 nm”, suele referirse a una clase tecnológica o a un hito de escalado, más que a que todos los elementos del transistor midan literalmente esa cifra.

Aun así, el documento funciona como una declaración de intenciones: Corea del Sur quiere poner por escrito que su industria aspira a liderar la siguiente fase, incluso cuando el escalado obliga a lidiar con problemas cada vez más complejos: variabilidad, fugas, disipación térmica, límites del interconectado y una fabricación que roza el terreno donde la física se vuelve el mayor adversario.

Nueve tecnologías “núcleo”: del proceso al chip de Inteligencia Artificial y la computación cuántica

El roadmap no se limita a decir “iremos a nodos más pequeños”. Según ETNews, su propósito es contribuir a reforzar la competitividad tecnológica e industrial a largo plazo, dinamizar la investigación académica y orientar estrategias de formación de talento. Y para ello estructura sus previsiones en nueve tecnologías consideradas esenciales:

- Dispositivos y procesos de semiconductores

- Semiconductores para Inteligencia Artificial

- Interconexión óptica

- Sensores semiconductores de conexión inalámbrica

- Semiconductores de conexión cableada

- PIM (Processing-In-Memory)

- Packaging

- Computación cuántica

- (y el conjunto de líneas tecnológicas agrupadas en el documento como ejes de evolución)

El listado revela un cambio de mentalidad: el futuro no depende solo del “nodo”, sino del sistema completo. La velocidad ya no se gana únicamente con transistores más pequeños, sino con mejor interconexión, memoria más rápida, empaquetado avanzado y arquitecturas pensadas para cargas específicas, especialmente en Inteligencia Artificial.

Memoria: DRAM más fina, HBM con más capas y un salto de ancho de banda

Donde el roadmap resulta más llamativo para el mercado es en memoria, el gran cuello de botella de la era de la Inteligencia Artificial. Las previsiones citadas por ETNews apuntan a:

- DRAM: reducción del circuito desde 11 nm hasta 6 nm.

- HBM (High-Bandwidth Memory): salto desde 12 capas y 2 TB/s hasta 30 capas o más y 128 TB/s.

Es una proyección agresiva, pero coherente con la dirección del sector: los aceleradores de Inteligencia Artificial y los sistemas de alto rendimiento están cada vez más condicionados por cuánto y cómo pueden mover datos, no solo por la potencia bruta de cálculo. En ese sentido, la evolución de HBM —más capas, más ancho de banda— se ha convertido en una carrera estratégica.

NAND: de 321 capas a 2.000 capas

El roadmap también pone cifras a un objetivo que, por ambicioso, parece diseñado para provocar: la NAND flash pasaría de las 321 capas actuales a un techo proyectado de 2.000 capas.

El mensaje es doble. Por un lado, la industria continúa apostando por el apilado vertical como vía de crecimiento. Por otro, deja caer que la escalada de complejidad (fabricación, rendimiento, costes) será inevitable, y que el almacenamiento seguirá siendo una pieza central tanto para centros de datos como para el ecosistema de dispositivos.

Chips de Inteligencia Artificial: del presente a “TOPS” de otra liga

En semiconductores para Inteligencia Artificial, ETNews recoge otra previsión que resume la lógica del roadmap: en 15 años se espera un salto sustancial en rendimiento medido en operaciones por segundo.

El documento compara el punto de partida —en el artículo se menciona una referencia de 10 TOPS por vatio— con un horizonte en el que los chips podrían llegar a 1.000 TOPS para aprendizaje y 100 TOPS para inferencia.

Más allá de las cifras, la interpretación es clara: el roadmap presupone que el crecimiento de la Inteligencia Artificial no será sostenible sin mejoras radicales en eficiencia y arquitectura, y que la industria coreana quiere estar en el centro de esa transformación.

Un roadmap que también es política industrial

Este tipo de documentos no son solo predicciones: funcionan como herramienta de coordinación entre industria, universidades y administraciones. ETNews subraya que el Instituto planea actualizar y revisar el roadmap de forma periódica, ampliando el alcance según necesidades tecnológicas.

En un contexto global marcado por la competencia entre bloques —Estados Unidos, China, Corea del Sur, Taiwán y Europa—, una hoja de ruta de este tipo actúa como mensaje hacia dentro (prioridades de inversión, formación de talento) y hacia fuera (intención de liderazgo). Y, sobre todo, confirma una realidad: el futuro del chip no se explica con una única métrica. Será una combinación de nuevas estructuras de transistor, integración 3D, memorias más avanzadas, interconexión y packaging.

Preguntas frecuentes

¿Qué significa que el sector entre en la “era del ångström” en semiconductores?

Implica trabajar en escalas de décimas de nanómetro y abordar límites físicos cada vez más exigentes. En la práctica, suele ser una forma de describir una nueva etapa de miniaturización y arquitectura, no solo un cambio de unidad.

¿Un chip de “0,2 nm” es literal o es una forma de hablar de nodos tecnológicos?

Normalmente es una referencia a una “clase” de nodo y a un conjunto de mejoras tecnológicas. Los nombres de nodo no siempre se corresponden con una única dimensión física exacta dentro del transistor.

¿Qué es CFET y por qué se menciona como clave para 2040?

CFET es una arquitectura de transistor complementario que busca seguir aumentando densidad y eficiencia cuando el escalado tradicional se vuelve insuficiente. Suele asociarse a estrategias de integración más vertical.

¿Por qué HBM y el ancho de banda importan tanto en la era de la Inteligencia Artificial?

Porque muchos sistemas de Inteligencia Artificial están limitados por el movimiento de datos. Aumentar capas y ancho de banda en HBM ayuda a alimentar el cómputo con más datos y menos cuellos de botella.

vía: etnews