# DHRUV64: India's First 1.0 GHz, 64-bit dual-core Microprocessor

15 December, 2025

### **Key Takeaways**

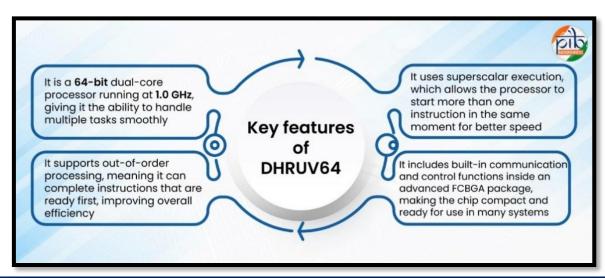

- **DHRUV64**, India's first homegrown **1.0 GHz**, **64-bit dual-core microprocessor**, strengthens the indigenous processor pipeline.

- National Programmes like **Digital India RISC-V** give India the support needed to design, test and prototype indigenous chips, including DHRUV64.

- After DHRUV64 success, the next-generation Dhanush and Dhanush+ processors are now under development.

### **Introduction**

India has achieved a significant milestone in its semiconductor journey with the launch of DHRUV64. It is a fully indigenous microprocessor developed by the Centre for Development of Advanced Computing (C-DAC) under the Microprocessor Development Programme (MDP). DHRUV64 provides the nation a reliable, homegrown processor technology. It is capable of supporting strategic and commercial applications. It marks a major advancement in India's pursuit of self-reliance in advanced chip design.

#### Did you know?

Microprocessors are the brains of modern electronic devices such as mobiles, computers, automobiles, medical equipment, defence systems and satellites. For India, building and owning such core technologies is important to reduce reliance on foreign suppliers and support the growing electronics and digital economy.

DHRUV64 is built with modern architectural features. It delivers higher efficiency, enhanced multitasking capability and improved reliability. Its advanced design enables seamless integration with a wide range of external hardware systems. The processor's modern fabrication leverages technologies used for high-performance chips. This makes DHRUV64 suitable for sectors such as 5G infrastructure, automotive systems, consumer electronics, industrial automation and the Internet of Things (IoT).

Strategic Significance of DHRUV64 for India

**D**HRUV64 marks a major milestone in India's efforts to build a secure and self-reliant semiconductor ecosystem. It strengthens the nation's indigenous capability in advanced processor development. It supports the critical digital infrastructure and hence, reduces the long-term dependence on imported microprocessors.

India consumes around 20% of all the microprocessors manufactured globally. The development of DHRUV64 provides India's large talent base with a fully modern processor platform for advancement of semiconductor ecosystem in India.

Before DHRUV64, India had already begun expanding its indigenous microprocessor development ecosystem in recent years. Key examples include:

- SHAKTI (2018, IIT Madras): Designed for strategic, space, and defence applications;

- AJIT (2018, IIT Bombay): A microprocessor for industrial and robotics applications;

- **VIKRAM (2025, ISRO–SCL):** A processor developed for space applications such as navigation, guidance, and mission operations; engineered to withstand extreme space conditions;

- **THEJAS64 (2025, C-DAC):** Designed for industrial automation.

Developing indigenous processors such as the SHAKTI, AJIT, VIKRAM, THEJAS, and now the DHRUV64 is strategically significant. These processors drive the creation of an Indian processor ecosystem.

### DHRUV64's Impact on India's R&D and Innovation

- DHRUV64 provides a homegrown microprocessor technology designed for startups, academia, and industry to build, test, and scale indigenous computing products without relying on foreign processors.

- DHRUV64 supports prototype development for new system architectures at lower cost.

- India already has 20% of the world's chip design engineers. DHRUV64 further helps in building a strong pipeline of skilled semiconductor chip professionals.

- The success of DHRUV64 accelerates the roadmap for **Dhanush** and **Dhanush** processors. They are now under development phase.

## Rollout of DHRUV64 and India's Digital India RISC-V (DIR-V) Progress

The Government of India launched the Digital India RISC-V (DIR-V) Programme to advance the vision of Aatmanirbhar Bharat. It aims to establish India as a global hub for Electronics System Design and Manufacturing (ESDM). The initiative develops a complete portfolio of RISC-V-based microprocessors. These processors will power applications across industry, strategic sectors, and consumer technologies.

### RISC-V Open Architecture and Its Significance for India

RISC-V is an open architecture that provides a set of instructions for chip design. It involves no licence costs, which allows wider adoption through shared innovation by industry, start-ups and research institutions.

- It helps build a complete portfolio of indigenous microprocessors under the **DIR-V Programme** for use in various sectors.

- It encourages shared innovation by providing common tools and standards for developers, improving collaboration across research organisations and companies.

### DHRUV64 Driving India's Indigenous Chip Roadmap

The launch of DHRUV64 marks an important step in strengthening India's self-reliant microprocessor ecosystem. By utilising open-source architecture, DHRUV64 eliminates licence costs. This supports long-term deployment across platforms.

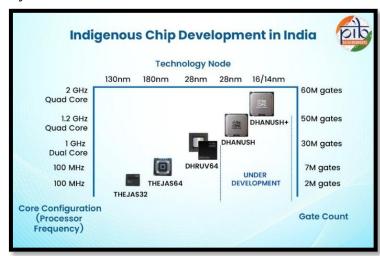

DHRUV64 is the **third chip** fabricated under the DIR-V Programme with an overall aim to enable creation of Microprocessors for the future in India.

- **The first chip**, *THEJAS32*, fabricated at the Silterra facility in Malaysia.

- The second chip, THEJAS64, manufactured domestically at Semiconductor Lab (SCL) Mohali.

- In addition, the design, implementation, and fabrication of **DHANUSH64 and DHANUSH64+** System on a Chip (SoC) variants are currently under development.

The rollout of DHRUV64 demonstrates India's growing capability in developing indigenous microprocessor technologies. The continued progress of the DIR-V initiative reinforces the nation's commitment to building a strong microprocessor ecosystem.

# **Institutional Ecosystem Driving Processor Development**

1

India's efforts to build a strong semiconductor ecosystem are supported by a coordinated institutional framework led by key national agencies. These institutions provide policy direction and programme support that enable the design, and development of indigenous processors.

**Ministry of Electronics and Information Technology (MeitY):** MeitY plays a central role in advancing India's processor and semiconductor initiatives. It guides national programmes through policy support, funding and long-term planning under schemes; such as the Microprocessor Development Programme, DIR-V, C2S and the India Semiconductor Mission. These measures have strengthened the country's design ecosystem and enabled steady progress in indigenous processor development.

**C-DAC:** C-DAC leads the design of India's indigenous processors. It creates processor Intellectual Properties (IPs), System-on-Chips (SoCs), development boards and related tools under MeitY's flagship programmes, supporting the growth of a complete domestic processor ecosystem. The organisation is now advancing work on the next processors in the RISC-V roadmap, **Dhanush** and **Dhanush+**. These upcoming processors are expected to strengthen India's homegrown RISC-V ecosystem. It expands the range of indigenous options available for strategic, and commercial use.

# Key National Programmes Supporting Indigenous Chip Design

The Government of India has launched flagship programmes that strengthen design capability, expand research infrastructure and encourage innovation across academia, startups and industry.

**India Semiconductor Mission (ISM):** The India Semiconductor Mission (ISM), launched in December 2021 under Meity, provides structured support and works with global companies to bring large semiconductor investments into the country. As of 2025, the mission has approved **ten projects across six states**, with a total

<sup>1</sup> https://amritmahotsav.negd.in/presentation/day5/VEGA%20%20Processors.pdf

investment commitment of ₹1.60 lakh crore.<sup>2</sup> Through ISM, India is positioning itself as a competitive player in the global semiconductor ecosystem.

**Digital India RISC-V (DIR-V) Programme**: The Digital India RISC-V (DIR-V) Programme, launched in **April, 2022** has played a central role in advancing India's indigenous chip design efforts. It enabled the development of advanced RISC-V processors in India. The programme aims to bring researchers, startups and industry into a shared design ecosystem, improving collaboration and innovation.

**Chips to Startup (C2S) Programme**: The C2S Programme, launched by MeitY in **2022**, is a capacity-building initiative implemented across **113** institutions, including 100 academic and R&D organisations and 13 startups and MSMEs. The programme has an outlay of ₹250 crore for a five-year period. The C2S Programme aims to generate **85,000** industry-ready manpower and create vibrant fabless chip design ecosystem in the country. <sup>3</sup>

**Design Linked Incentive (DLI) Scheme:** The DLI Scheme, launched in **2021**, aims to offer financial incentives as well as design infrastructure support across various stages of development and deployment of semiconductor design for Integrated Circuits (ICs), Chipsets, System on Chips (SoCs), Systems & IP Cores and semiconductor linked design over a period of 5 years.<sup>4</sup>

**Indian Nanoelectronics Users Programme- idea to innovation (INUP-i2i)**: This programme, launched by MeitY, gives researchers, students and startups access to national nanofabrication facilities at leading institutions. It provides hands-on training in chip and device fabrication, helping innovators understand how semiconductor components are built. A total of **49** familiarization workshops, **42** Hands-on-training workshops, **36** Industrial trainings and **10** Hackathons have been conducted. More than **8000** skilled manpower has been trained and around **348** short term and **220** mid-term R&D projects are being supported under the project.<sup>5</sup>

### **Conclusion**

India's progress in indigenous processor development reflects a strong commitment to **Aatmanirbhar Bharat** in the semiconductor sector. DHRUV64 powered and supported by national programmes such as DIR-V, C2S, ISM, DLI and INUP-i2i, the processor showcases the country's growing capability to design, develop and prototype advanced processors. With coordinated efforts across MeitY, C-DAC, academic institutions and industry, India is building the talent, research strength and infrastructure needed for long-term leadership in advanced technologies. The progress from **THEJAS32 to DHRUV64**, and the ongoing development of **Dhanush and Dhanush+**, illustrates a confident national pathway toward indigenous processor innovation and technological self-reliance.

### References

### Ministry of Electronics and IT

- https://www.meity.gov.in/static/uploads/2024/12/10fcadec462c330211502fed3d24ea83.pdf

- <a href="https://www.pib.gov.in/PressReleaseIframePage.aspx?PRID=1946003&reg=3&lang=2">https://www.pib.gov.in/PressReleaseIframePage.aspx?PRID=1946003&reg=3&lang=2</a>

- https://www.pib.gov.in/PressReleasePage.aspx?PRID=2159727&reg=3&lang=2

### **India Semiconductor Mission**

https://ism.gov.in/design-linked-incentive

#### **Press Information Bureau Backgrounders**

• <a href="https://www.pib.gov.in/FactsheetDetails.aspx">https://www.pib.gov.in/FactsheetDetails.aspx</a>?Id=149242&reg=3&lang=2

#### **VEGA Processors**

<sup>&</sup>lt;sup>2</sup> https://www.pib.gov.in/FactsheetDetails.aspx?Id=149242&reg=3&lang=2

https://sansad.in/getFile/annex/266/AU2938 TeCVaq.pdf?source=pqars

https://chips-dli.gov.in/DLI/Faq

https://www.pib.gov.in/PressReleasePage.aspx?PRID=1710134&reg=3&lang=2 https://www.pib.gov.in/PressReleasePage.aspx?PRID=2159727&reg=3&lang=2 https://chips-dli.gov.in/DLI/HomePage

<sup>&</sup>lt;sup>5</sup> https://www.meity.gov.in/static/uploads/2024/12/10fcadec462c330211502fed3d24ea83.pdf (page 180)

| • https://vegaprocessors.in/                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special Service and Features                                                                                                                                                                    |

| • https://www.pib.gov.in/PressReleasePage.aspx?PRID=2107709®=3⟨=2                                                                                                                               |

| Design Linked Incentive  • https://chips-dli.gov.in/DLI/Faq                                                                                                                                     |

| Ministry of Commerce & Industry  • <a href="https://www.pib.gov.in/PressReleasePage.aspx?PRID=1710134&amp;reg=3&amp;lang=2">https://www.pib.gov.in/PressReleasePage.aspx?PRID=1710134®=3⟨=2</a> |

| Rajya Sabha  • https://sansad.in/getFile/annex/266/AU2938 TeCVaq.pdf?source=pqars                                                                                                               |

| PIB Research                                                                                                                                                                                    |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |

|                                                                                                                                                                                                 |